El grupo de diseño microelectrónico y test de prototipos del Departamento de Ingeniería Electrónica y Biomédica de la Universidad de Barcelona (UB) está liderando la integración, layout y fabricación de prototipos (tape-out) de los procesadores DRAC, así como el desarrollo de las plataformas de test para los mismos. DRAC es un proyecto de investigación con el objetivo de producir procesadores RISC-V y diferentes aceleradores tratando de lograr el máximo rendimiento posible minimizando el consumo de energía. Para lograrlo, una correcta selección del proceso tecnológico donde se fabricarán los procesadores es obligatoria, ya que afecta el rendimiento, el consumo energético y los costes de fabricación. En el proyecto DRAC se han estudiado varias tecnologías, pero la seleccionada es el proceso tecnológico 22 nm FD-SOI (22FDX) de Globalfoundries (GF), ya que nos permite llegar a frecuencias de reloj por encima de 1GHz, nos da diferentes opciones para reducir el consumo de energía y los costes de fabricación son relativamente bajos.

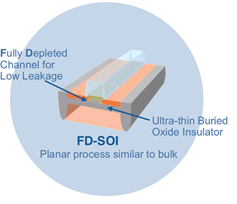

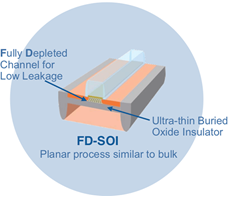

Figura 1: Vista esquemática de un transistor en la tecnología de 22 nm FD-SOI de GF. Imagen obtenida de link (15/Dic/2020)

GF es una fundición de semiconductores (del inglés foundry) estadounidense con sede en Santa Clara, California, Estados Unidos. GF tiene cinco plantas de fabricación de obleas de 200 mm en Singapur, dos plantas de 300 mm una en Alemania y otra en Singapur, y tres plantas en los Estados Unidos: una planta de 200 mm en Vermont (donde es el mayor empleador privado) y dos plantas de 300 mm en Nueva York. Sin embargo, la fundición en la que se desarrolla el proceso de 22 nm está ubicada en Dresde, Alemania.

El proceso 22FDX ofrece la mejor combinación de rendimiento, consumo de energía y coste para dispositivos de Internet de las cosas (IoT), telefonía móvil convencional, conectividad de RF, redes, etc. La plataforma "22FDX ™" ofrece un rendimiento similar a FinFET y eficiencia energética a coste comparable al de las tecnologías planares de 28nm, proporcionando una solución óptima para los mercados antes mencionados. 22DFX es un proceso existente desde 2015. Por lo tanto, es suficientemente estable y maduro.

Este proceso proporciona una gran flexibilidad en el binomio potencia / velocidad gracias al control de la tensión del sustrato, que será positivo (Fordward Body Bias - FBB) para dispositivos en los que se desea incrementar la eficiencia y negativo (Reverse Body Bias - RBB) para reducir el consumo por fugas. El proceso 22FDX también ofrece transistores con diferentes tensiones umbral para aumentar estas posibilidades. Así, como es común en procesos sub-micrónicos, se encuentran disponibles transistores con tensión umbral baja (SLVT / LVT), tensión umbral media (RVT / HVT) y tensión umbral alta (ULL).

Los procesadores DRAC tienen como objetivo aumentar el rendimiento (es decir, llegar a frecuencias de reloj superiores a 1 GHz), lo que significa que se utilizarán transistores de tensión umbral baja (SLVT / LVT) y FBB para el procesador, las memorias SRAM y algunos bloques analógicos como el PLL. Sin embargo, lograr un consumo de energía bajo es siempre una necesidad, por lo tanto, también se implementarán técnicas de baja consumo como “clock gating”, el escalado dinámico de voltaje y frecuencia (DVFS) y la reducción del voltaje de polarización del sustrato (polarización cero). Además, cualquier bloque / circuito adicional sin restricciones de velocidad agresivas usaría transistores de tensión umbral media (RVT / HVT).

Los prototipos (tape-outs) se fabricarán a través del consorcio Europractice utilizando los servicios Multi-Project-Wafer (MPW). El primer prototipo estará disponible a fines de 2021, mientras que el segundo prototipo estará disponible a fines de 2022.