En el diseño del primer chip del proyecto (Sargantana) han participado 3 grupos del proyecto DRAC: Barcelona Supercomputing Center (BSC), Universitat Politècnica de Catalunya (UPC) y la Universitat de Barcelona (UB). Además, han participado también el Instituto Politécnico Nacional (IPN) de Méjico y el Instituto de Microelectronica de Barcelona (IMB-CNM), en particular el grupo ICAS (Integrated Circuits and Systems).

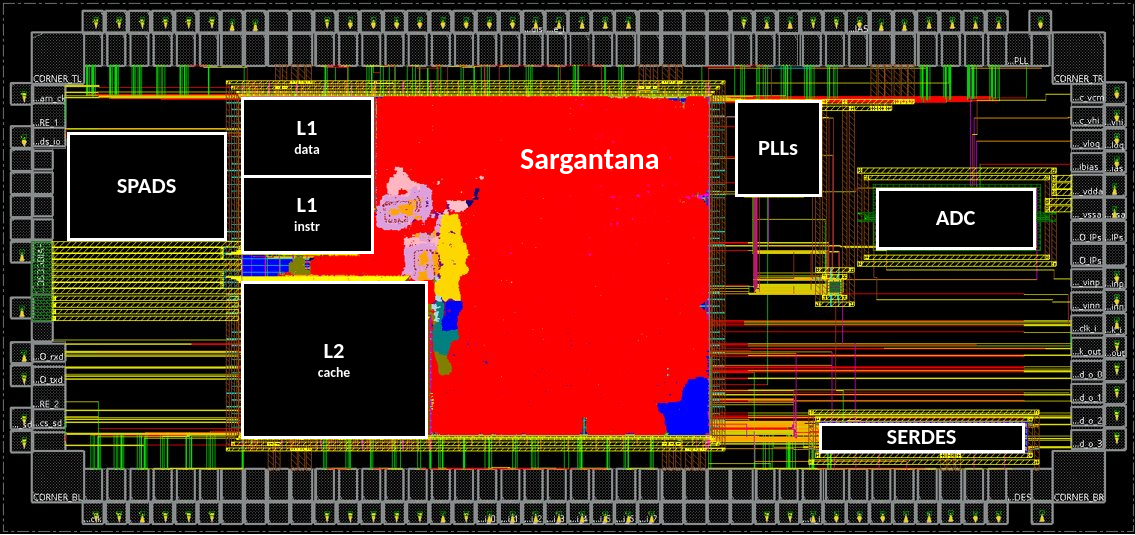

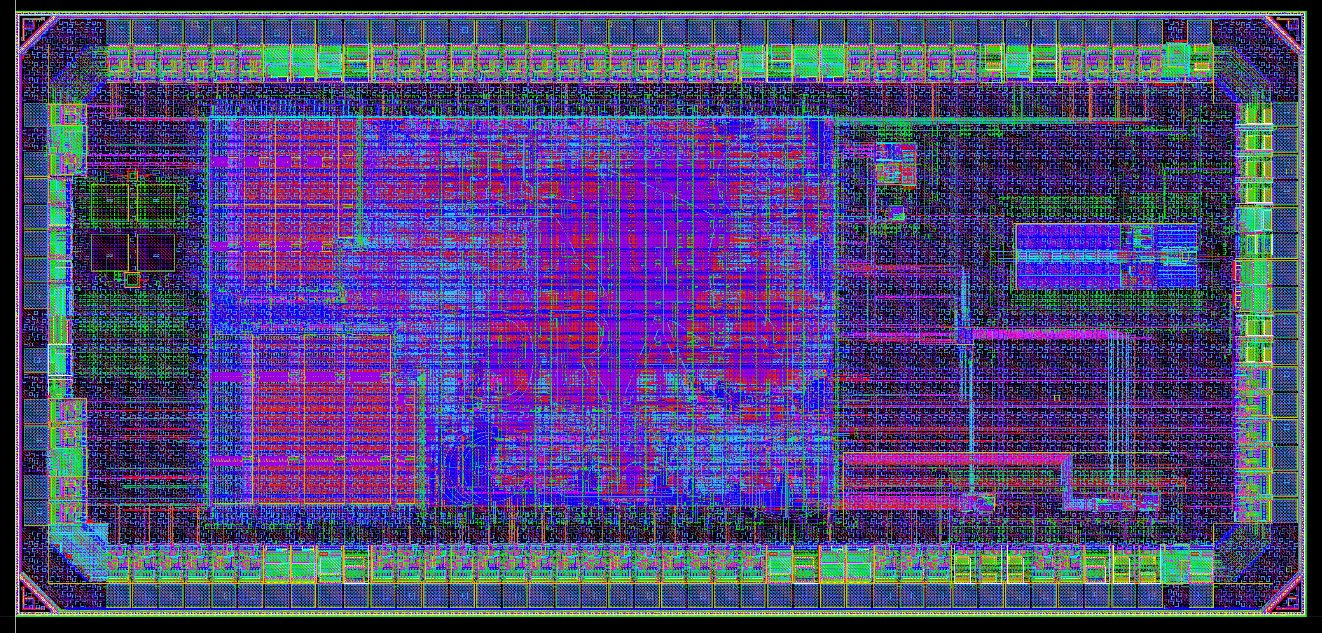

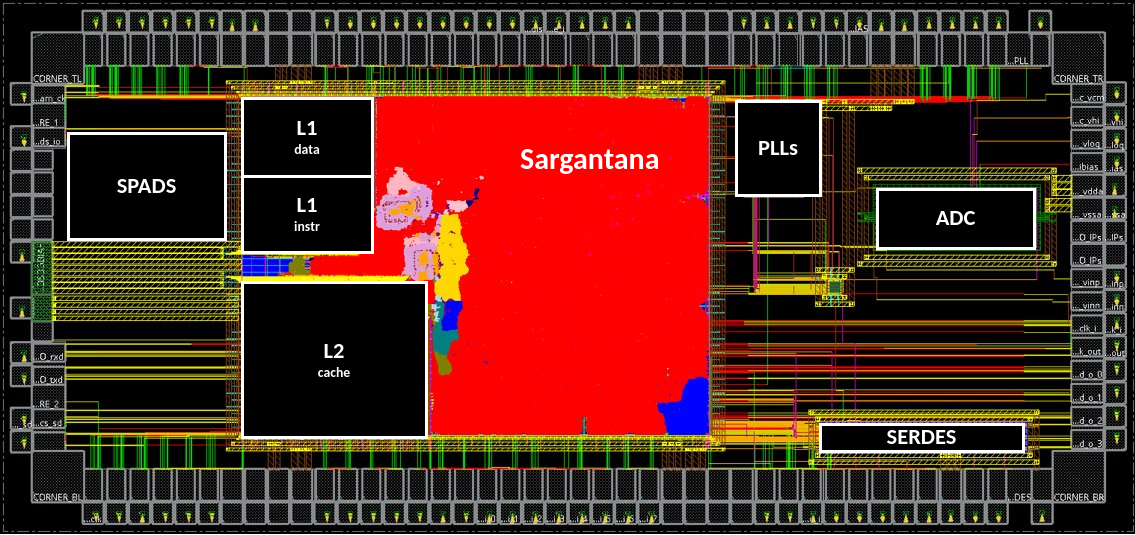

El primer chip diseñado en el proyecto se envió a fabricar el 18 de febrero de 2022. El chip se muestra en la Figura 1a, mide 2.49 mm de ancho por 1.17 mm de alto, lo que da un área total de 2.91 mm2, y ha sido diseñado en la tecnología de 22 nm de GlobalFoundries. Aparte del procesador RISC-V Sargantana diseñado en el proyecto, contiene distintos diseños necesarios para el correcto funcionamiento del procesador. Estos circuitos se muestran en la Figura 1b.

El chip pretende caracterizar las IPs suministradas por Synopsys, como las memorias y las celdas digitales, el procesador Sargantana y las IPs analógicas diseñadas por los distintos grupos involucrados en el proyecto. La contribución de cada grupo de investigación al chip (Figura 1b) se detalla a continuación:

Sargantana: Procesador RISC-V, diseñado por el BSC e IPN, con un pipeline de 7 etapas, usa la ISA (del inglés Instruction Set Architecture) RV64IMAFD y contiene una unidad vectorial de enteros para genómica. Más detalles del procesador pueden encontrarse en el siguiente link.

Phase-locked loop (PLL): Un PLL es un circuito para generar un reloj a alta frecuencia para el procesador. En este chip se han integrado dos PLLs, lo que nos permite tener una solución extra en caso de que uno de ellos no funcione correctamente. Los PLLs han sido diseñados por el grupo ICAS del IMB-CNM y por la UPC respectivamente.

SerDes: Un SerDes, o serializador/deserializador, es un circuito comúnmente utilizado en comunicaciones de alta frecuencia. Este circuito ha sido diseñado por la UPC.

Convertidor Analógico/Digital: Diseño del grupo ICAS del IMB-CNM, previamente publicado en el siguiente link.

Bloque configuración SPI: Diseño del grupo ICAS del IMB-CNM que permite configurar las distintas IPs analógicas.

Single Photon Avalanche Diodes (SPADs): Los SPADs son fotodetectores de estado sólido y pueden ser usados para generar números aleatorios. El grupo de diseño de la UB ha integrado un par de estructuras SPAD en el chip.

Síntesis Física: La síntesis física del chip se ha llevado a cabo por parte de la UB, detalles sobre los pasos seguidos en el “place & route” (es decir, colocar los diferentes bloques, conectarlos y comprobar que el diseño cumple las normas de diseño del fabricante) se pueden encontrar en el siguiente link. Tras estas etapas, se realizaron dos pasos adicionales: análisis de tiempo estático (STA) y el análisis de potencia.

Para los estudios STA, se creó un modelo con los elementos parásitos del chip para estudiar si el diseño cumple con las limitaciones de tiempo impuestas por los diseñadores. Los resultados muestran que el procesador puede funcionar con una frecuencia de hasta 1.4 GHz.

Los estudios de análisis de potencia se realizan asumiendo que el procesador tiene una actividad del 10% y comprobando el consumo estático por el mejor, típico y peor caso a distintas temperaturas. En todos estos casos, los resultados muestran que la distribución de potencia es correcta y la caída de IR puede corregirse.