A l'era d'Internet de les coses (IoT), els sistemes de detecció intel·ligent ubics contribueixen significativament al paradigma de Big Data i estan incorporant gradualment algun tipus de computació in-situ (edge computing). Aquestes aplicacions de sensat intel·ligent exigeixen convertidors d'analògic-digitals (ADC) de baixa potència i alta resolució, amb relacions de senyal-a-soroll-i-distorsió (SNDR) de l'ordre dels 90dB, però amb valors reals d'amplada de banda que generalment no excedeixen el rang dels kHz. Els moduladors de sobre-mostreig Delta-Sigma (DSM) s'adeqüen bé a aquests requisits i les seves implementacions en forma de capacitats commutades (SC) acostumen a mostrar-se més robustes contra les variacions de la tecnologia CMOS que els seus equivalents de temps continu. No obstant això, el nombre de DSMs SC fabricats amb SNDR>90dB i valors d'amplada de banda superiors a 20kHz és relativament escàs [1]. De fet, aquests convertidors de dades d'alta resolució de propòsit general no solen establir la xifra absoluta de figura de mèrit de Schreier d'última generació FOMS = SNDR+10*log (Freqüència de mostreig/Consum d'energia). A la pràctica, les seves implementacions en CMOS han d'enfrontar aspectes complexos del disseny com soroll flicker, no linealitat i injecció de càrrega dels interruptors, desaparellament tecnològic, no linealitat del guany dels OpAmps, jitter del rellotge o acoblament de soroll a través de les alimentacions, entre d'altres. Fins i tot el valor de la FOMS per si sol no pot tenir en compte qüestions crítiques com l'estabilitat davant de la variabilitat tecnològica i de la temperatura, la necessitat de calibrar el circuit o l'ús de multiplicadors d'alimentació per controlar els interruptors SC.

En aquest context de disseny, s'han emprat diverses estratègies d'arquitectura DSM per millorar el rang dinàmic: filtrat de soroll d'alt ordre (> 4) en llaç únic, que és propens a la inestabilitat; moduladors de múltiples etapes (MASH) que tendeix a patir desaparellament tecnològic en el filtre de reconstrucció; i els DSM Zoom guiats per SAR, el control intern del fons d'escala dels quals introdueix glitches i excés d'harmònics fora de banda. A nivell de circuit CMOS, les contribucions de soroll flicker al rang dels kHz s'atenuen habitualment en topologies diferencials mitjançant l'ús de chopping malgrat el rissat i els harmònics resultants.

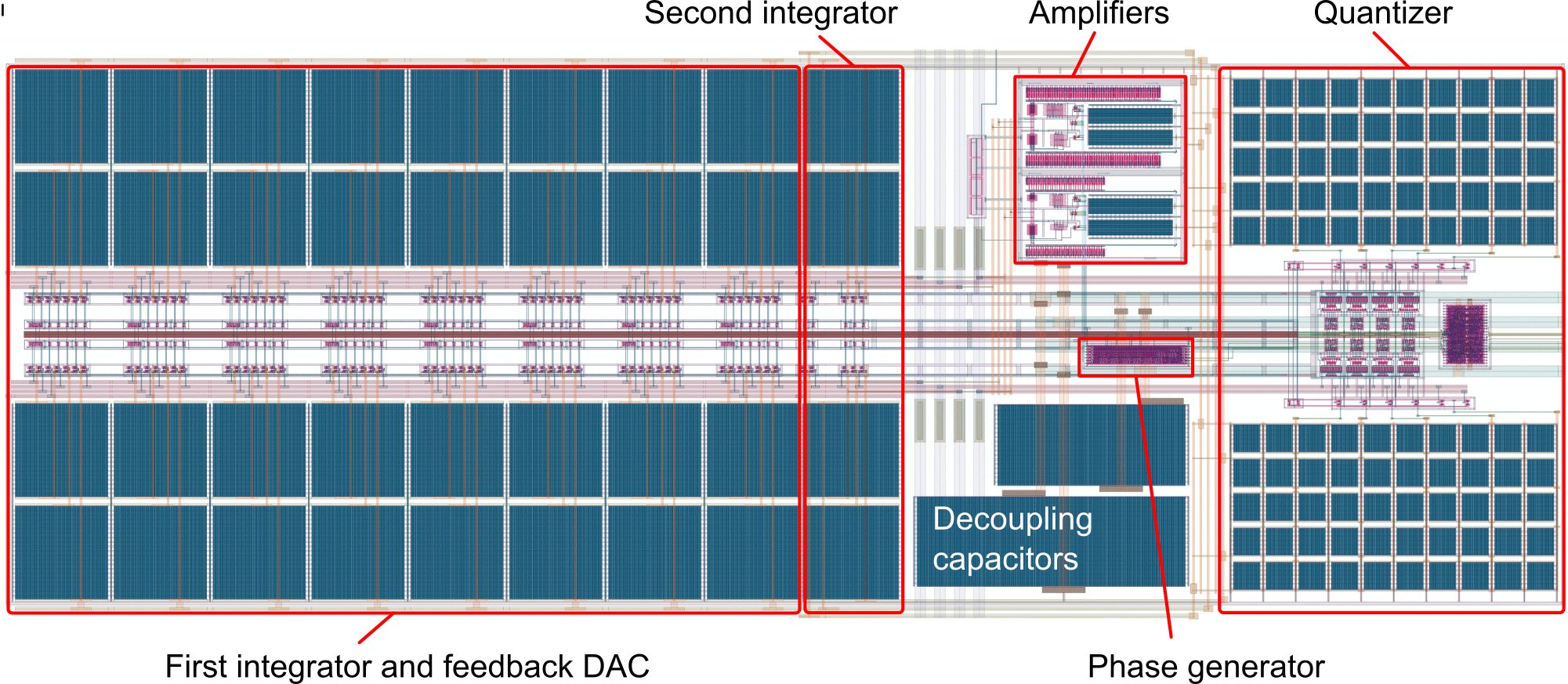

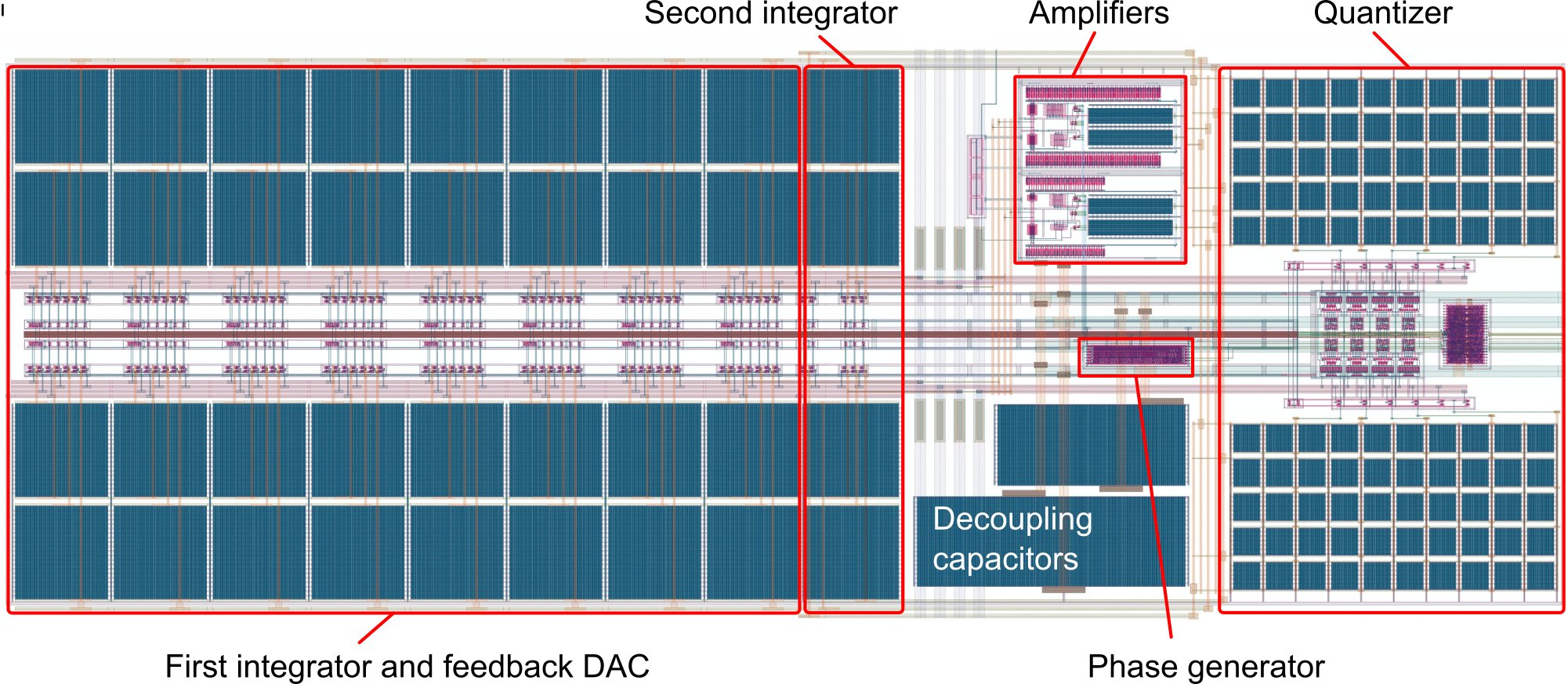

El bloc IP ADC de baixa potència i alta resolució proposat es basa en un DSM SC de 9 nivells i de segon ordre que supera els 90dB de pic SNDR, amb una amplada de banda de 50kHz i cancel·lació de soroll flicker basada en un doble mostreig correlat (CDS). Els circuits DSM CMOS incorporen OpAmps de Classe AB commutats i de mirall variable (VMA), que eviten tant l'ús de multiplicadors per als interruptors com el 50% de l'energia estàtica, juntament amb un quantificador SC flash multi-bit. En comparació amb els DSMs SC de llaç únic d’última generació, la millora en l’eficiència energètica es tradueix en un augment de 6dB a 12dB de la FOMS. A més, la cancel·lació de soroll de 1/f presentada no causa l'arrissat i els harmònics típics de les solucions chopping. A diferència dels DSMs Zoom, aquest modulador no genera un excés d'harmònics i presenta una alta puresa espectral per amplituds d'entrada properes al fons d’escala.

El bloc IP inclou el propi DSM juntament amb el decimador digital per reduir el mostreig fins quasi a la freqüència Nyquist i una interfície AXI Lite estàndard (no es mostra a la Figura 1). Gràcies a la combinació de quantificació multi-bit, ordre de filtre baix i factor de sobre-mostreig moderat, l'IP ADC estalvia aproximadament el 75% de l'energia associada a la dinàmica del senyals interns en comparació als DSMs d'un sol bit equivalents. A més, el mecanisme de cancel·lació de soroll flicker del CDS permet una millora neta de 10dB de la FOMS. A nivell de circuit CMOS, l'ús de VMA es tradueix en una baixa sensibilitat davant dels corners tant de procés tecnològic com de temperatura d'operació.

Aquest bloc IP convertidor de dades s'ha portat a tres nodes de tecnologia CMOS diferents: XFAB 1.8V 180nm, TSMC 1.2V 65nm i GF 0.8V 22nm. Totes les implementacions apunten a una SNDR de 95dB i una amplada de banda de 50kHz a 12.8MS/s, amb una reducció en consum d'energia i en àrea de silici de {741,632,197} µW i {0.202,0.186,0.043} mm2, respectivament. Les FOMS resultants són 176.0 dB. 178.8 dB i 179.6 dB i són a l'estat de l'art d'aquests mòduls ADC. Actualment, s'han caracteritzat les mostres de l'IP de 180nm [2], mentre que la versió en silici de 65nm es validarà experimentalment en breu i el disseny en 22nm està llest per enviar a la seva fabricació de prototips.

[1] B. Murmann, ADC Performance Survey 1997-2021, http://web.stanford.edu/~murmann/adcsurvey.html.

[2] A. Suanes, L. Terés, M. Dei i F. Serra-Graells, ADC modulador Delta-Sigma SC Delta-Sigma sin arranque de 0.8mW 50kHz 94.6dB-SNDR con cancelación de ruido de parpadeo, Actas del Simposio Internacional IEEE sobre Circuits and Systems (ISCAS), pp. 1-5, Daegu, Corea, maig 2021, https://doi.org/10.1109/ISCAS51556.2021.9401688.