En la era de Internet de las cosas (IoT), los sistemas de detección inteligente ubicuos contribuyen significativamente al paradigma de Big Data y están incorporando gradualmente algún tipo de computación in-situ (edge computing). Estas aplicaciones de sensado inteligente exigen convertidores de analógico-digitales (ADC) de baja potencia y alta resolución, con relaciones de señal-a-ruido-y-distorsión (SNDR) del orden de los 90dB, pero con valores reales de ancho de banda que generalmente no exceden el rango de los kHz. Los moduladores de sobre-muestreo Delta-Sigma (DSM) se adecúan bien a estos requisitos y sus implementaciones en forma de capacidades conmutadas (SC) acostumbran a mostrarse más robustos contra las variaciones de la tecnología CMOS que sus equivalentes de tiempo continuo. Sin embargo, el número de DSMs SC fabricados con SNDR>90dB y valores de ancho de banda superiores a 20kHz es relativamente escaso [1]. De hecho, estos convertidores de datos de alta resolución de propósito general no suelen establecer la cifra absoluta de figura de mérito de Schreier de última generación FOMS = SNDR+10*log (Frecuencia de muestreo/Consumo de energía). En la práctica, sus implementaciones en CMOS deben enfrentar aspectos complejos del diseño como ruido flicker, no linealidad e inyección de carga de los interruptores, desemparejamiento tecnológico, no linealidad de ganancia de OpAmps, jitter del reloj o acoplamiento de ruido a través de las alimentaciones, entre otros. Incluso el valor de la FOMS por sí solo no puede tener en cuenta cuestiones críticas como la estabilidad frente a la tecnología y a la temperatura, la necesidad de calibrar el circuito o el uso de multiplicadores de alimentación para controlar los interruptores SC.

En dicho contexto de diseño, se han empleado varias estrategias de arquitectura DSM para mejorar el rango dinámico: filtrado de ruido alto orden (> 4) en lazo único, que es propenso a la inestabilidad; moduladores de múltiples etapas (MASH) que tienden a sufrir desemparejamiento tecnológico en el filtro de reconstrucción; y los DSMs Zoom guiados por SAR, cuyo control interno del fondo de escala introduce glitches y un exceso de armónicos fuera de banda. A nivel de circuito CMOS, las contribuciones de ruido flicker en el rango de los kHz se atenúan habitualmente en topologías diferenciales mediante el uso de chopping a pesar del rizados y los armónicos resultantes.

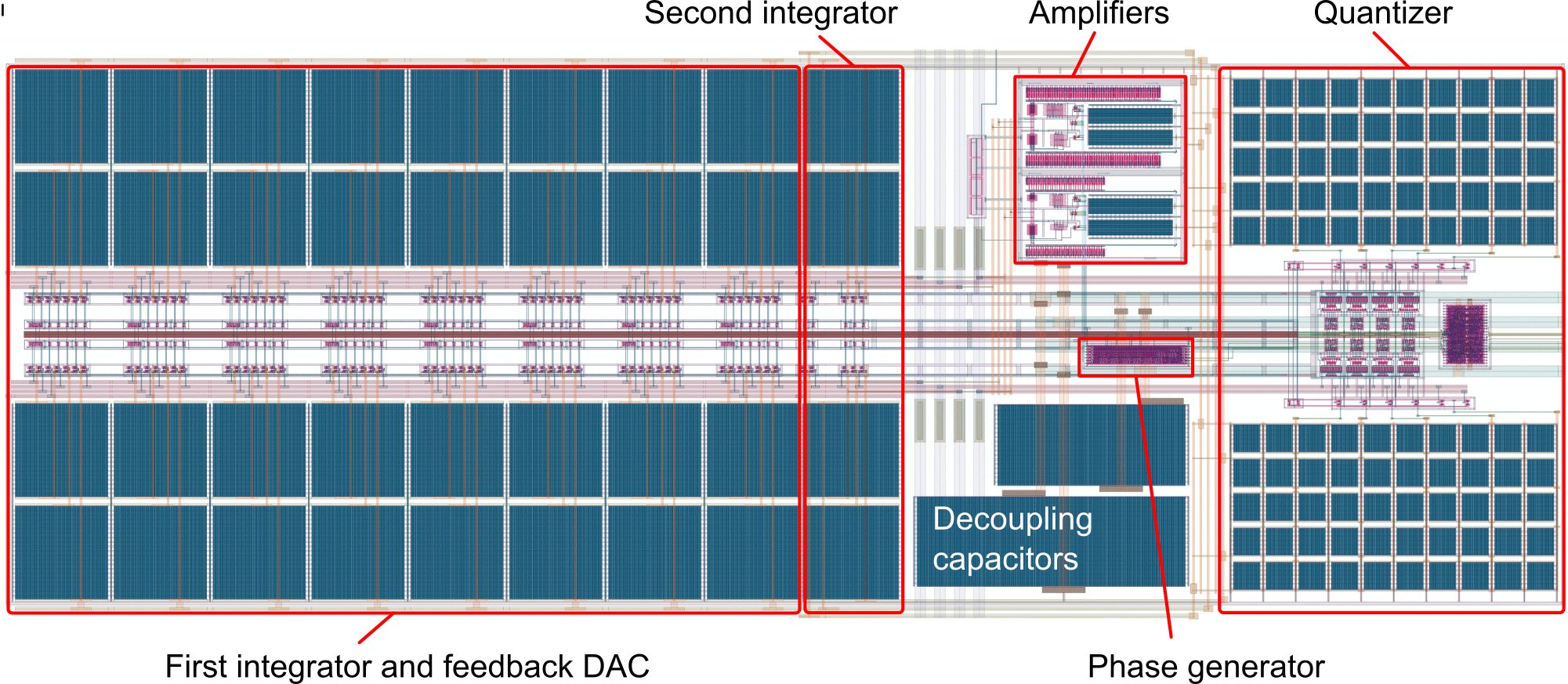

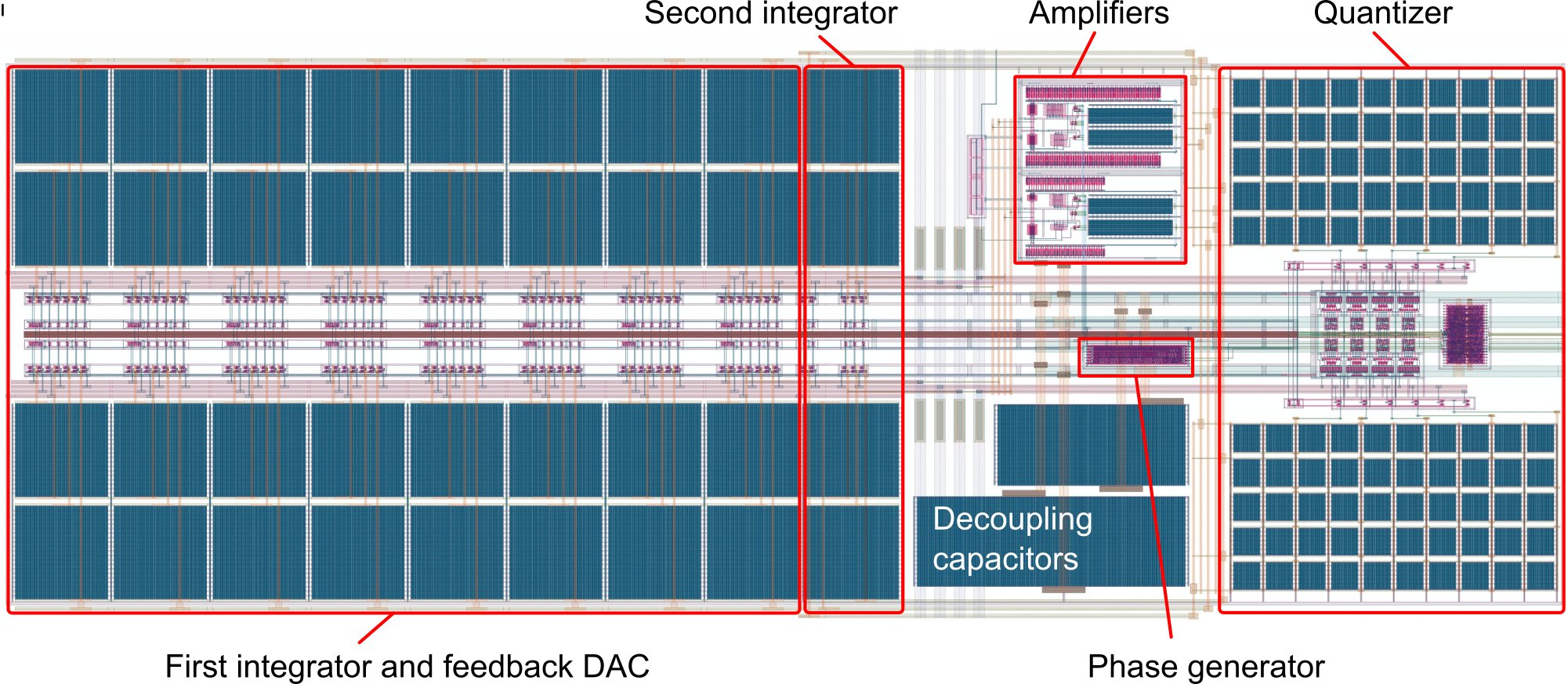

El bloque IP ADC de baja potencia y alta resolución propuesto se basa en un DSM SC de 9 niveles y de segundo orden que supera los 90dB de pico SNDR, con un ancho de banda de 50kHz y cancelación de ruido flicker basada en un doble muestreo correlado (CDS). Los circuitos DSM CMOS incorporan OpAmps de Clase AB conmutados y de espejo variable (VMA), que evitan tanto el uso de multiplicadores para los interruptores cómo el 50% de la energía estática, junto con un cuantificador SC flash multi-bit. En comparación con los DSMs SC de lazo único de última generación, la mejora en la eficiencia energética se traduce en un aumento de 6dB a 12dB en FOMS. Además, la cancelación de ruido de 1/f presentada no causa el rizado y los armónicos típicos de las soluciones chopping. A diferencia de los DSMs Zoom, este modulador no genera un exceso de armónicos y presenta una alta pureza espectral para amplitudes de entrada cercanas al fondo de escala.

El bloque de IP incluye el propio DSM junto con el decimador digital para reducir el muestreo hasta casi la frecuencia de Nyquist y una interface AXI Lite estándar (no se muestra en la Figura 1). Gracias a la combinación de cuantificación multi-bit, orden de filtro bajo y factor de sobre-muestreo moderado, el IP ADC ahorra aproximadamente el 75% de la energía asociada a la dinámica de señales internas en comparación con los DSMs de un solo bit equivalentes. Además, el mecanismo de cancelación de ruido flicker del CDS permite una mejora neta de 10dB en FOMS. A nivel de circuito CMOS, el uso de VMA se traduce en una baja sensibilidad frente a los corners tanto de proceso tecnológico como de temperatura de operación.

Este bloque IP conversor de datos se ha portado a tres nodos de tecnología CMOS diferentes: XFAB 1.8V 180nm, TSMC 1.2V 65nm y GF 0.8V 22nm. Todas las implementaciones apuntan a una SNDR de 95dB y a un ancho de banda de 50kHz a 12.8MS/s, con una reducción en consumo de energía y en área de silicio de {741,632,197} µW y {0.202,0.186,0.043} mm2, respectivamente. Las FOMS resultantes son 176.0 dB. 178.8 dB y 179.6 dB y están en el estado del arte de estos módulos ADC. Actualmente, se han caracterizado las muestras del IP de 180nm [2], mientras que la versión de 65nm se testeará en breve y el diseño en 22nm está listo para enviar a su fabricación de prototipos.

[1] B. Murmann, ADC Performance Survey 1997-2021, http://web.stanford.edu/~murmann/adcsurvey.html.

[2] A. Suanes, L. Terés, M. Dei y F. Serra-Graells, A 0.8mW 50kHz 94.6dB-SNDR Bootstrapping-Free SC Delta-Sigma Modulator ADC with Flicker Noise Cancellation, Actas del IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, Daegu, Corea, mayo 2021, https://doi.org/10.1109/ISCAS51556.2021.9401688.