Projecte 1: Disseny i implementació d'un processador fora d'ordre

L'objectiu principal d'aquesta tasca és dissenyar, codificar, verificar i construir el processador fora d'ordre que serà el motor de tot el projecte i on se li s'incorporaran els diferents acceleradors que es desenvoluparan. El joc d'instruccions triat és el RISC-V, que és un joc d'instruccions modern que permet afegir acceleradors a el processador amb un joc d'instruccions específic per a tal fi. D'altra banda, utilitzar RISC-V facilita que el nostre processador pugui executar programes ja que podem utilitzar les eines desenvolupades per RISC-V, des del sistema operatiu fins als compiladors.

Projecte 2: Seguretat post-quàntica i tècni ques de virtualització

ques de virtualització

Molts dels criptosistemes estàndard actuals són vulnerables a atacs executats des d'ordinadors quàntics. El NIST americà està intentant trobar els millors esquemes criptogràfics entre els que no són vulnerables a atacs clàssics i quàntics. En aquest projecte s'analitzaran diferents esquemes candidats i es dissenyaran les extensions segures per a aquests esquemes per a ser incorporats en el processador basat en RISC-V. També es desenvoluparan i implementaran tècniques de seguretat clàssica com la randomització per aconseguir tenir un processador fora d'ordre segur i la implementació dels nivells (rings) de seguretat hardware juntament amb el suport hardware dels mecanismes de virtualització presents en l'ISA de RISC- V.

Projecte 3: Arquitectures de computadors per accelerar aplicacions d'anàlisi genòmic

L'objectiu principal d'aquest projecte és el disseny de noves arquitectures paral·leles d'alt rendiment per al processat i anàlisi de dades genòmiques a gran escala. Aquestes aplicacions són un component molt rellevant en les aplicacions actuals i futures de la medicina personalitzada: la fase de seqüenciació és una part rellevant del pipeline de la majoria d'anàlisi de les dades genòmiques i la seva reducció té un impacte directe en el tractament de les dades de salut. En aquest projecte s'estudiaran els requisits a nivell d'arquitectura d'aquestes aplicacions i es desenvoluparà un nou accelerador basat en un processador vectorial per a aquest tipus d'aplicacions. Finalment, s'establirà un cicle de co-disseny entre els desenvolupadors de les aplicacions d'anàlisi genòmic i els dissenyadors de l'accelerador permetent una major eficiència i rendiment.

Projecte 4: Acceleració d'aplicacions d'automoció amb computació aproximada en tecnologia FDSOI

L'arribada de la conducció autònoma requereix de l'ús de hardware relativament senzill (i econòmic) que doni un rendiment molt alt dins d'un límit de consum molt estricte per complir amb els requeriments dels sistemes d'automoció. Els sistemes d'alt rendiment actuals que podrien donar el rendiment necessari, ho fan amb un consum molt alt. En aquest sentit, i atès que els processos de conducció autònoma són necessàriament heurístics i aproximats, aquest projecte està enfocat a dissenyar un accelerador que, en comptes d'utilitzar hardware determinista per donar resultats aproximats, o unitats aproximades per implementar operacions aritmètiques deterministes, utilitzi la computació aproximada per a funcions complexes i la tecnologia FDSOI (orientada a baix consum) que pot introduir alteracions en els resultats quan s'opera a baixa tensió d'alimentació, de manera que, sense empitjorar la precisió global del procés de predicció, es puguin implementar sistemes de conducció autònoma amb una millor combinació de rendiment i consum, i sense afectar la requerida fiabilitat. En particular, aquest projecte dissenyarà i implementarà la unitat de càlcul que s'indica i definirà detalladament la seva integració en futures generacions del processador europeu, que ataca els segments de supercomputació i automoció.

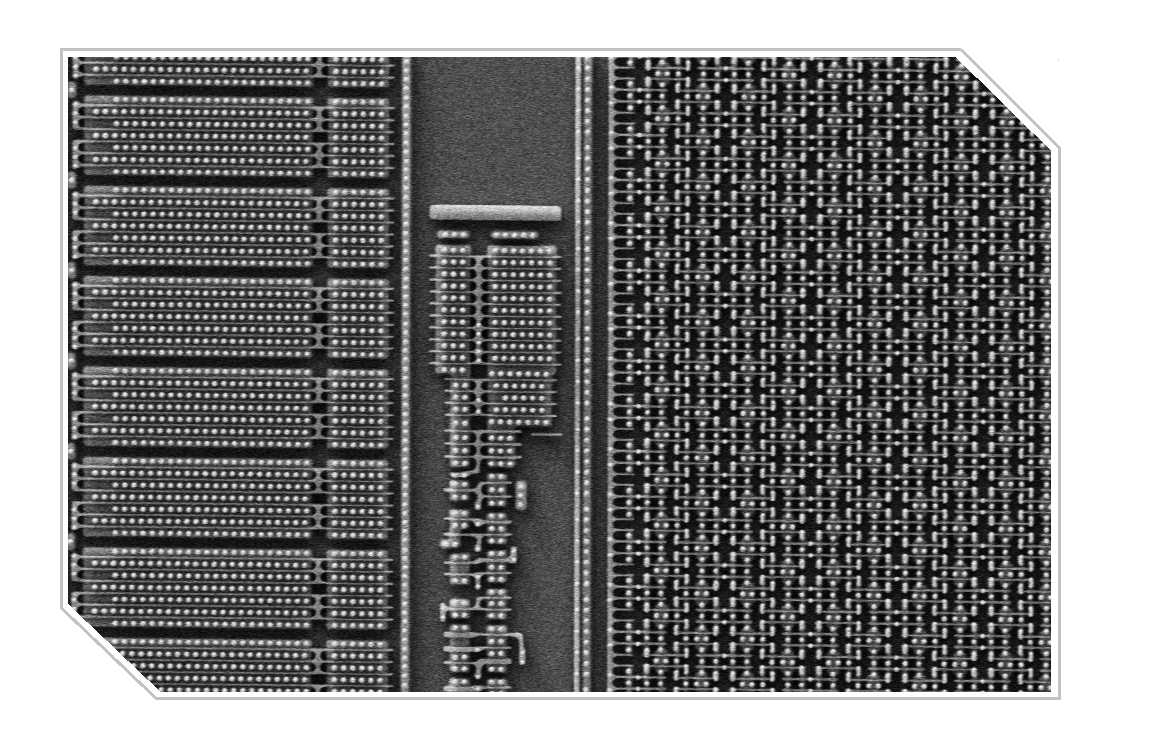

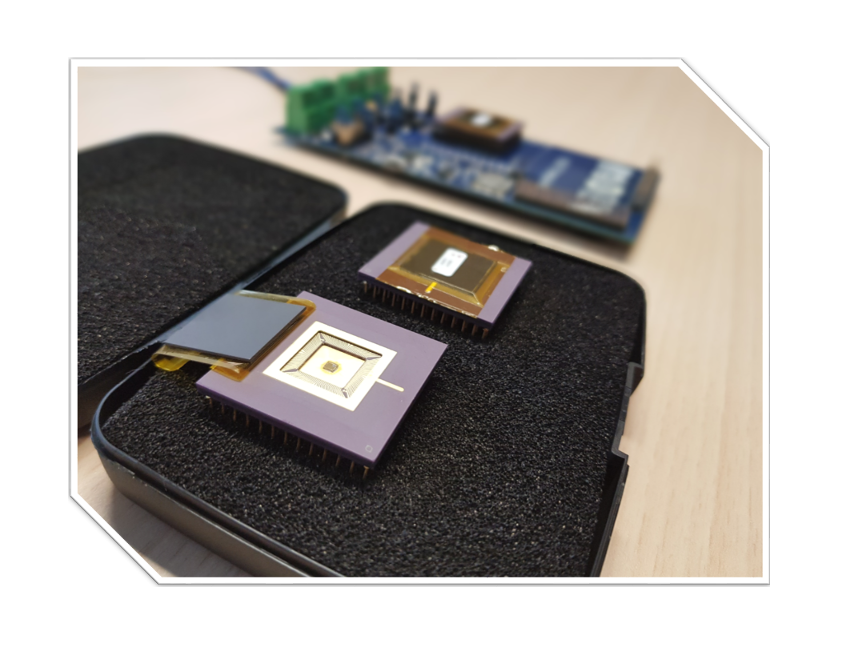

Projecte 5: Integració, layout i fabricació de prototips i plataforma de test

de prototips i plataforma de test

En aquest projecte es coordinarà i gestionarà l'accés a les diferents tecnologies desenvolupades en el marc d'aquesta agrupació tecnològica. En particular, s'han d'integrar els diferents blocs necessaris per fabricar el processador RISC-V i diferents acceleradors dissenyats. També es desenvoluparà la plataforma de testing per poder comprovar que el processador dissenyat funciona correctament.

Projecte 6: Difusió i transferència tecnològica

La comunicació dels resultats d'aquesta agrupació tecnològica, així com l'explotació de la IP resultant en forma de contractes de llicència, són claus per a l'èxit de el projecte. La pàgina web del projecte inclou la descripció del projecte i dona visibilitat als resultats del projecte. Es destinarà un esforç a difondre la tecnologia desenvolupada entre totes les universitats de Catalunya mitjançant la preparació d'un kit educacional basat en processadors RISC-V que podran fer servir els estudiants universitaris de grau, màster i doctorat.