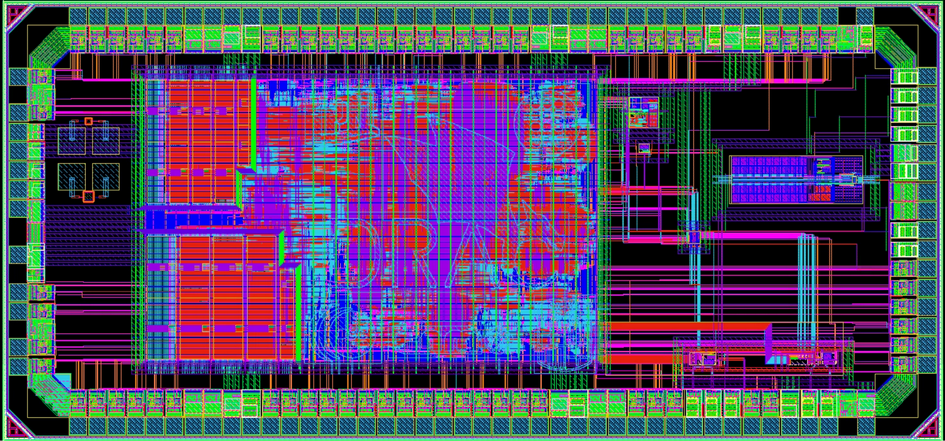

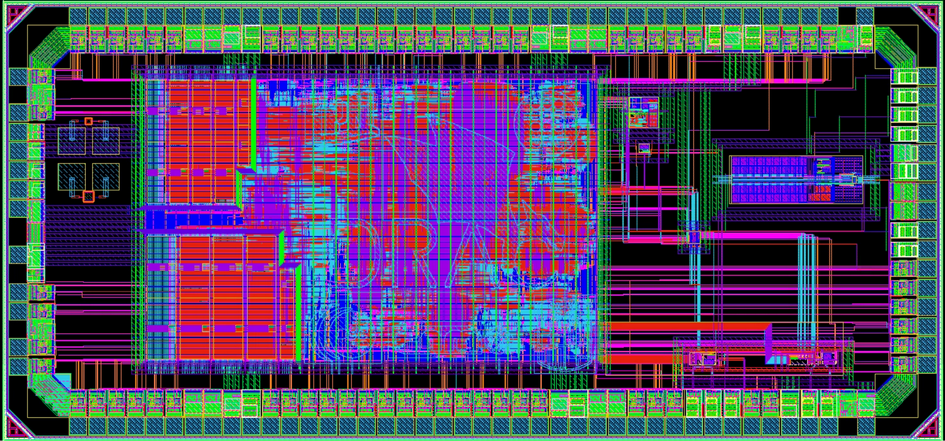

Nos complace anunciar que la tercera generación de los procesadores Lagarto ha sido enviada a fabricar via Europractice en el nodo tecnológico GlobalFoundries 22nm. Este diseño está basado en el repertorio de instrucciones (ISA por sus siglas en inglés) abierto RISC-V y es un diseño desarrollado conjuntamente por investigadores del BSC, CIC-IPN, CNM, UAB, UB, UPC y URV.

Este nuevo diseño se denomina Sargantana (nombre de lagarto en aragonés y catalán) e integra un núcleo escalar Lagarto con múltiples IPs analógicas. Sargantana es el primer procesador de la familia Lagarto que supera la barrera del gigahercio en la frecuencia de trabajo.

Principales novedades de Sargantana respecto a DVINO, la segunda generación de procesadores Lagarto:

- Reestructuración del diseño segmentado lineal. De acuerdo con las simulaciones realizadas, se espara un 36% de mejora en el IPC de las aplicaciones de interés.

- Diseño segmentada más profundo para alcanzar una frecuencia de 1.2GHz en el cas típico.

- Soporte para instrucciones de coma flotante de precisión simple y doble (extensiones F y D a RISC-V).

- Nueva unidad vectorial de 128 bits para operaciones enteras y específicas para genómica.

- Accesos a memoria no bloqueantes con hasta 16 fallos en vuelo (hasta 2 bloques de cache).

- Nuevo controlador de memoria de alta velocidad SerDes (entre 2 y 8 Gbps).

- Nuevo controlador bootROM personalizado para Sargantana.

- Nueva IP personalizada para convertir señales analógicos a digitales (A2D converter) con alta resolución de 16 bits, cancelación de ruído de parpadeo e interficie estándar AXI4-lite.

- Nueva IP personalizada diodo de avalancha de un solo fotón (SPAD por sus siglas en inglés) para generar números aleatoreos.

Detalles del procesador Sargantana:

- Diseño segmentado Lagarto Hun, 7 etapas, en orden, RV64IMAFD ISA, ISA privilegiada 1.11.

- VPU entera para aplicaciones de genómica, longitud vectorial de 128 bits, ISA vectorial 0.7.1.

- PLL interno. DVINO puede operar a 600, 400, 300 y 200MHz.

- PLL (Phase Locked Loop) integrado en el chip diseñado y simulado para generar frecuencias entre 600MHz y 2.2GHz.

- Diseño in-house de la cache de instrucciones L1 y la PMU (performance monitoring unit).

- Caches L1 de datos y L2 del proyecto lowRISC 0.2.

- Múltiples controladores de periféricos esenciales: JTAG, UART, SPI, bootROM, SerDes e HyperRAM.

- Diseño in-house de un debug-ring basado en JTAG.

- Nodo tecnológico: GF 22nm.

- Area: 2.89mm2.

Detalles de la primera generación del procesador Lagarto:

- Nota de premsa de la segunda generación de Lagarto (2021): https://drac.bsc.es/ca/media/news/tech-dvino-la-segona-generacio-dels-processadors-lagarto-enviat-fabricar-europractice

- Nota de premsa de la primera generación de Lagarto (2019): https://www.bsc.es/news/bsc-news/the-bsc-coordinates-the-manufacture-the-first-open-source-chip-developed-spain