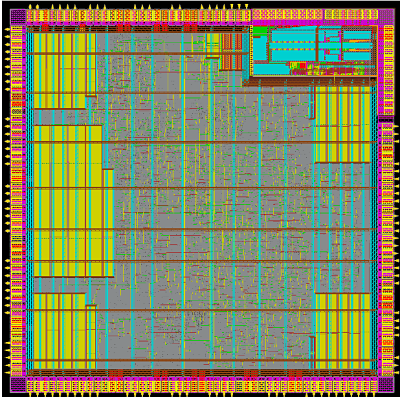

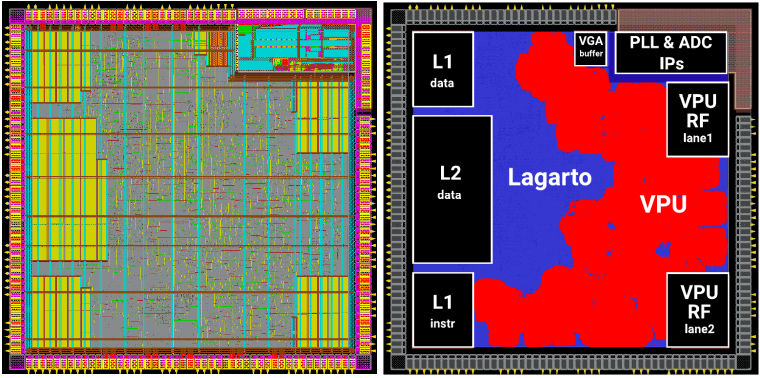

Ens complau anunciar que la segona generació dels processadors Lagarto ha sigut enviada a fabricar via Europractice en el node tecnològic TSMC 65nm. Aquest disseny està basat en el repertori d'instruccions (ISA per les seves sigles en anglès) obert RISC-V i és un disseny conjunt desenvolupat per investigadors del BSC, CIC-IPN, CNM i UPC.

Aquest nou disseny s'anomena DVINO (DRAC Vector IN-Order) i integra un nucli escalar Lagarto amb el processador vectorial (VPU per les seves sigles en anglès) Hydra.

Principals novetats a DVINO respecte a la primera generació de processadors Lagarto:

- Reestructuració del disseny segmentat en ordre. D'acord amb les simulacions realitzades, s’espera un 15% de millora en l'IPC de les aplicacions d'interès.

- Actualització de la ISA entera a la versió 2.1 i de la ISA privilegiada a la versió 1.11.

- Nova VPU amb 2 lanes seguint les extensions vectorials de RISC-V versió 0.7.1.

- Integració d'un PLL al xip. Permet un increment de 3x en la freqüència del rellotge.

- Nous controladors: SDRAM, HyperRAM, VGA.

- Nova IP personalitzada per convertir senyals analògics a digitals (A2D converter) amb alta resolució.

- Increment d’àrea de 3.5x en el mateix node tecnològic.

Detalls del processador DRAC Vector IN-Order (DVINO):

- Disseny segmentat Lagarto Hun, 5 etapes, en ordre, RV64IMA ISA, ISA privilegiada 1.11.

- Hydra 2-lane VPU, longitud vectorial de 4096 bits, ISA vectorial 0.7.1.

- PLL intern. DVINO pot executar a 600, 400, 300 i 200MHz.

- Disseny in-house de la cache d'instruccions L1 i la PMU (performance monitoring unit).

- Caches L1 de dades i L2 del projecte lowRISC 0.2.

- Múltiples controladors: JTAG, UART, SPI, VGA, SDRAM i Hyperram.

- Disseny in-house d'un debug-ring basat en JTAG.

- Node tecnològic: TSMC 65nm.

- Àrea: 8.6mm2.

Detalls de la primera generació del disseny Lagarto: