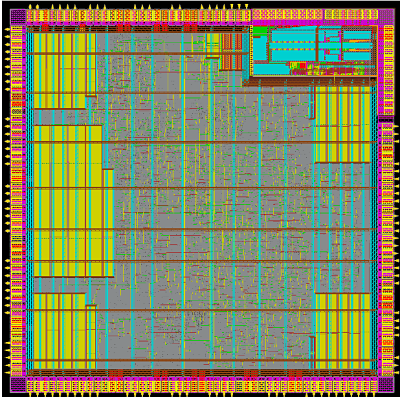

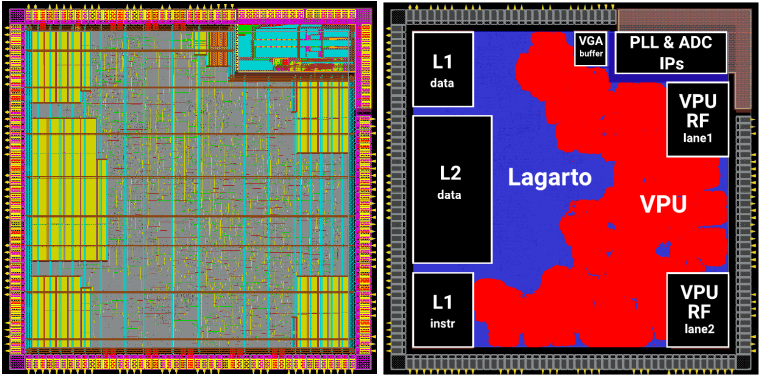

Nos complace anunciar que la segunda generación de los procesadores Lagarto ha sido enviada a fabricar vía Europractice en el nodo tecnológico TSMC 65nm. Este diseño está basado en el repertorio de instrucciones (ISA por sus siglas en inglés) abierto RISC-V y es un diseño desarrollado conjuntamente por investigadores del BSC, CIC-IPN, CNM y UPC.

Este nuevo diseño se denomina DVINO (DRAC Vector IN-Order) e integra un núcleo escalar Lagarto con el procesador vectorial (VPU por sus siglas en inglés) Hydra.

Principales novedades de DVINO respecto a la primera generación de procesadores Lagarto:

-

Reestructuración del diseño segmentado lineal. De acuerdo con las simulaciones realizadas, se espera un 15% de mejora en el IPC de las aplicaciones de interés.

-

Actualización de la ISA entera a la versión 2.1 y de la ISA privilegiada a la versión 1.11.

-

Nueva VPU con 2 lanes siguiendo las extensiones vectoriales de RISC-V versión 0.7.1.

-

Integración de un PLL al chip. Permite un incremento de 3x en la frecuencia del reloj.

-

Nuevos controladores: SDRAM, HyperRAM, VGA.

-

Nueva IP personalizada para convertir señales analógicas a digitales (A2D converter) con alta resolución.

-

Incremento del área de 3.5x en el mismo nodo tecnológico.

Detalles del procesador DRAC Vector IN-Order (DVINO):

- Diseño segmentado Lagarto Hun, 5 etapas, en orden, RV64IMA ISA, ISA privilegiada 1.11.

- Hydra 2-lane VPU, longitud vectorial de 4096 bits, ISA vectorial 0.7.1.

- PLL interno. DVINO puede operar a 600, 400, 300 y 200MHz.

- Diseño in-house de la caché de instrucciones L1 y la PMU (performance monitoring unit).

- Cachés L1 de datos y L2 del proyecto lowRISC 0.2.

- Múltiples controladores: JTAG, UART, SPI, VGA, SDRAM e Hyperram.

- Diseño in-house de un debug-ring basado en JTAG.

- Nodo tecnológico: TSMC 65nm.

- Área: 8.6mm2.

Detalles de la primera generación del procesador Lagarto: