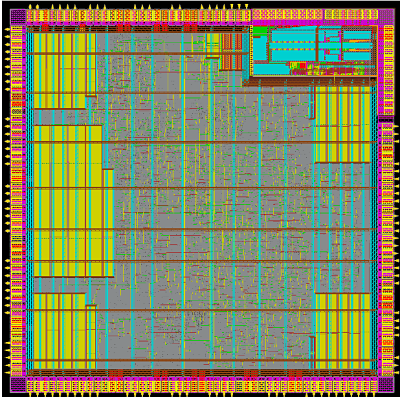

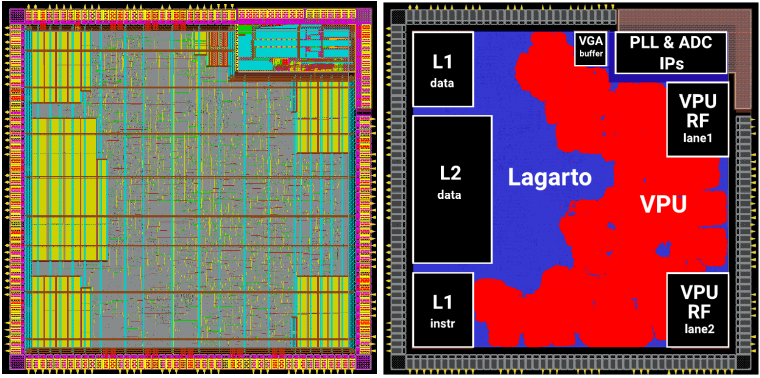

We are pleased to announce that the second generation of the Lagarto processor series has been submitted for fabrication in TSMC 65nm technology node via Europractice. This design is based on the open source instruction set architecture (ISA) RISC-V and is a design jointly developed by researchers from BSC, CIC-IPN, CNM and UPC.

This new design is called DVINO (DRAC Vector IN-Order) and integrates a Lagarto scalar core together with a Hydra Vector Processing Unit (VPU).

Main novelties of DVINO with respect to the first generation of the Lagarto series:

- Re-factored in-order core pipeline with an expected 15% IPC improvement with simulated benchmarks.

- Updated integer ISA to version 2.1 and privileged ISA to version 1.11.

- Added new 2-lane VPU supporting RISC-V vector extension version 0.7.1.

- Integrated on-chip PLL with up to 3x increase in clock frequency.

- Added new controllers: SDRAM, HyperRAM, VGA.

- Added custom 16-bit high-res analog-to-digital converter (ADC) IP.

- 3.5x increase in area in the same technology node.

DRAC Vector IN-Order (DVINO) processor details:

- Lagarto Hun scalar pipeline, 5-stage, in-order, RV64IMA ISA, privileged ISA 1.11.

- Hydra 2-lane VPU, 4096-bit vector length, vector ISA 0.7.1

- Internal PLL. DVINO can run at 600, 400, 300 and 200MHz.

- In-house L1 instruction cache and PMU (performance monitoring unit).

- L1 data and L2 caches from Untethered lowRISC version 0.2.

- Multiple controllers: JTAG, UART, SPI, VGA, SDRAM and Hyperram.

- In-house JTAG-based debug-ring

- Technology node: TSMC 65nm

- Area: 8.6mm2

First generation Lagarto design details: