Ens complau anunciar que la tercera generació dels processadors Lagarto ha sigut enviada a fabricar via Europractice en el node tecnològic GlobalFoundries 22nm. Aquest disseny està basat en el repertori d'instruccions (ISA per les seves sigles en anglès) obert RISC-V i és un disseny conjunt desenvolupat per investigadors del BSC, CIC-IPN, CNM, UAB, UB, UPC i URV.

Aquest nou disseny s'anomena Sargantana (nom de llangardaix en aragonès i català) i integra un nucli escalar Lagarto amb múltiples IPs analògiques. Sargantana és el primer processador de la família Lagarto que trenca la barrera del gigahertz en la freqüència de treball.

Principals novetats a Sargantana respecte a DVINO, la segona generació de processadors Lagarto:

- Reestructuració del disseny segmentat en ordre. D'acord amb les simulacions realitzades, s'espera un 36% de millora en l'IPC de les aplicacions d'interès.

- Disseny segmentat més profund per assolir la freqüència de 1.2GHz en el cas típic.

- Suport per instruccions de coma flotant de precisió simple i doble (extensions F i D a RISC-V).

- Nova unitat vectorial de 128 bits per operacions enteres i específiques per genòmica.

- Accessos a memòria no bloquejants amb fins a 16 fallades en vol (fins a 2 blocs de cache).

- Nou controlador de memòria d'alta velocitat SerDes (entre 2 i 8 Gbps).

- Nou controlador bootROM personalitzat per a Sargantana.

- Nova IP personalitzada per convertir senyals analògics a digitals (A2D converter) amb alta resolució de 16 bits, cancel·lació del soroll de parpelleig i interfície estàndard AXI4-lite.

- Nova IP personalitzada díode d'allau d'un sol fotó (SPAD per les seves sigles en anglès) per generar números aleatoris.

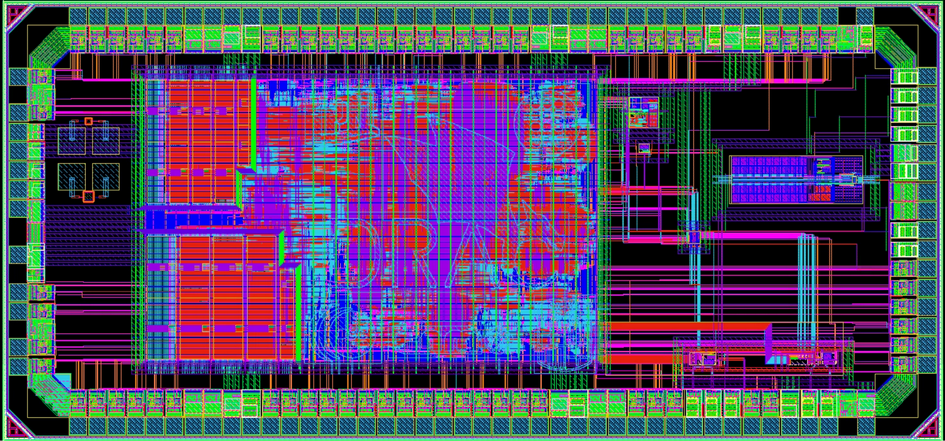

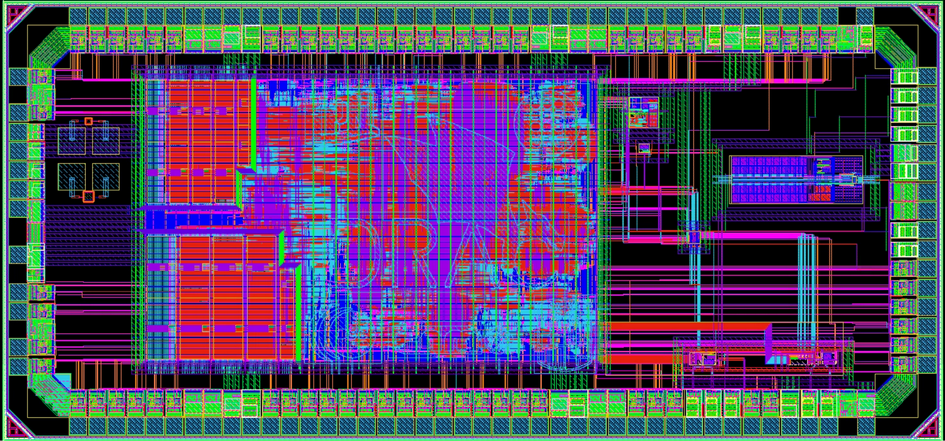

Detalls del processador Sargantana):

- Disseny segmentat Lagarto Hun, 7 etapes, en ordre, RV64IMAFD ISA, ISA privilegiada 1.11.

- VPU entera per aplicacions de genòmica, longitud vectorial de 128 bits, ISA vectorial 0.7.1.

- PLL (Phase Locked Loop) integrat al xip dissenyat i simulat per generar freqüències entre 600MHz i 2.2GHz.

- Disseny personalitzat de la cache d'instruccions L1 i la PMU (Performance Monitoring Unit).

- Caches L1 de dades i L2 del projecte lowRISC 0.2.

- Múltiples controladors de perifèrics essencials: JTAG, UART, SPI, bootROM, SerDes i HyperRAM.

- Disseny in-house d'un debug-ring basat en JTAG.

- Node tecnològic: GF 22nm.

- Àrea: 2.89mm2.

Detalls de les anteriors generacions del disseny Lagarto:

- Nota de premsa de la segona generació de Lagarto (2021): https://drac.bsc.es/ca/media/news/tech-dvino-la-segona-generacio-dels-processadors-lagarto-enviat-fabricar-europractice

- Nota de premsa de la primera generació de Lagarto (2019): https://www.bsc.es/news/bsc-news/the-bsc-coordinates-the-manufacture-the-first-open-source-chip-developed-spain