Los vehículos autónomos requieren de un software complejo que pueda procesar en tiempo real una enorme cantidad de datos (del orden de gigabytes por segundo) procedentes de diferentes sensores, tales como cámaras, LIDAR, entre otros. Estos datos se utilizan en los procesos de decisión relacionados con las diferentes tareas, como la predicción de trayectoria, por las que se utilizan algoritmos avanzados de inteligencia artificial. Uno de los programas más utilizados en conducción autónoma es Apollo.

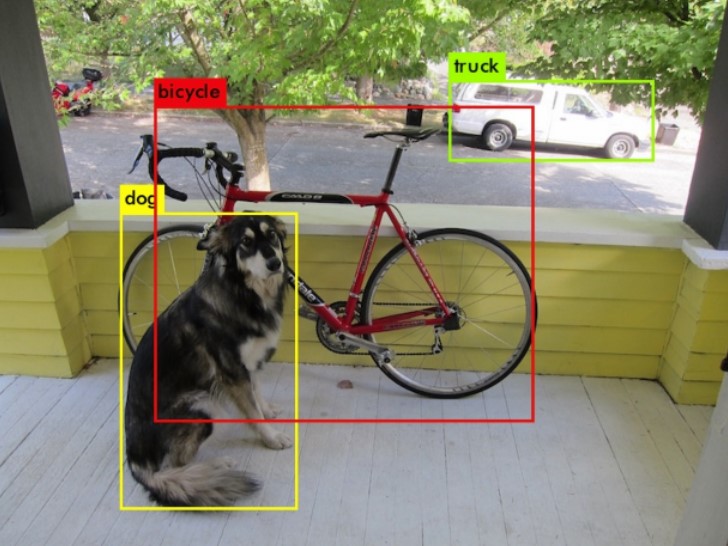

Apollo usa una variante de YOLO para la detección de objetos en imágenes, formando una de las principales partes del módulo de percepción. YOLO (You Only Look Once) es un sistema de detección ampliamente utilizado que se basa en una red neuronal convolucional (Convolutional Neural Network, CNN). Cada segundo, cada cámara en el vehículo captura múltiples imágenes y el detector de objetos las procesa secuencialmente.

Las redes neuronales en general, debido a su naturaleza, presentan una gran tolerancia a errores e imperfecciones. A partir de esta característica, investigadores de la Universitat Politècnica de Catalunya (UPC) y del Barcelona Supercomputing Center (BSC) tienen por objetivo, en el marco del proyecto DRAC, diseñar un acelerador de hardware que consuma menos energía aprovechando los principios del cálculo aproximado. Se consideran dos líneas:

-

Usar precisión reducida en la representación numérica. La implementación de YOLO utiliza por defecto números de coma flotante representados por 32 bits (FP32). Reducir el número de bits representa una reducción de potencia debido a que hay menos elementos e interconexiones que consumen energía en cada cálculo.

-

Usar unidades aritméticas aproximadas. Estas unidades se diseñan simplificando la estructura de las operaciones de suma y multiplicación, por ejemplo, de manera que sean más rápidas a pesar de que dan resultados inexactos para algunas combinaciones de entrada. Dada la tolerancia inherente de las CNN a los errores, se puede aprovechar esta característica para operar estas unidades a una tensión de alimentación más baja a la misma velocidad que unidades exactas convencionales, y por lo tanto reduciendo el consumo manteniendo las prestaciones.

Alternativas tales como FP16 (16 bits), FP8 (8 bits), o Posits-16 (16 bits) se han evaluado en términos de precisión en la detección de objetos usando la red YOLO. Por otra parte, varios sumadores y multiplicadores enteros y de coma flotante se han diseñado a nivel RTL para evaluar su precisión y ahorro de energía en diferentes condiciones de tensión y frecuencia de reloj.

Los resultados de estos análisis se utilizarán para la implementación del acelerador de hardware basado en estas aproximaciones. Este es el objetivo del proyecto P4 dentro de DRAC.