Uno de los objetivos fundamentales que persigue el diseño de procesadores es el de conseguir un alto nivel de rendimiento. A lo largo de los años han surgido diversas propuestas, tanto en la academia cómo en la industria, que han explorado ideas novedosas para conseguir este objetivo, aprovechando la evolución tecnológica dictada por la Ley de Moore. Sin embargo, el diseño de procesadores no ha dejado de ser una tarea desafiante en la que se busca mantener un balance entre complejidad y rendimiento.

En este sentido, los procesadores súper-escalares, los cuales son máquinas de procesamiento capaces de ejecutar múltiples instrucciones por ciclo de reloj, han demostrado ser eficaces al aprovechar el paralelismo a nivel de instrucción implementando técnicas de planificación dinámica, que conjugadas con una unidad de gestión de memoria eficiente, y aceleradores especializados, resultan en una alto aprovechamiento de los recursos hardware, alcanzando un porcentaje elevado durante la ejecución de instrucciones por ciclo de reloj.

En DRAC, se tiene como objetivo el diseño, verificación y fabricación de un procesador de alto rendimiento integrando varios aceleradores, además de otras prestaciones, en un mismo system-on-chip (SoC). Con la finalidad de alcanzar este objetivo, en un esfuerzo conjunto entre el BSC y el CIC-IPN, se ha propuesto el diseño e implementación del procesador Lagarto Ka, un procesador súper-escalar de 2-vías y 64-bits implementado en una microarquitectura de 12-etapas con ejecución fuera de orden basado en el conjunto de instrucciones de RISC-V.

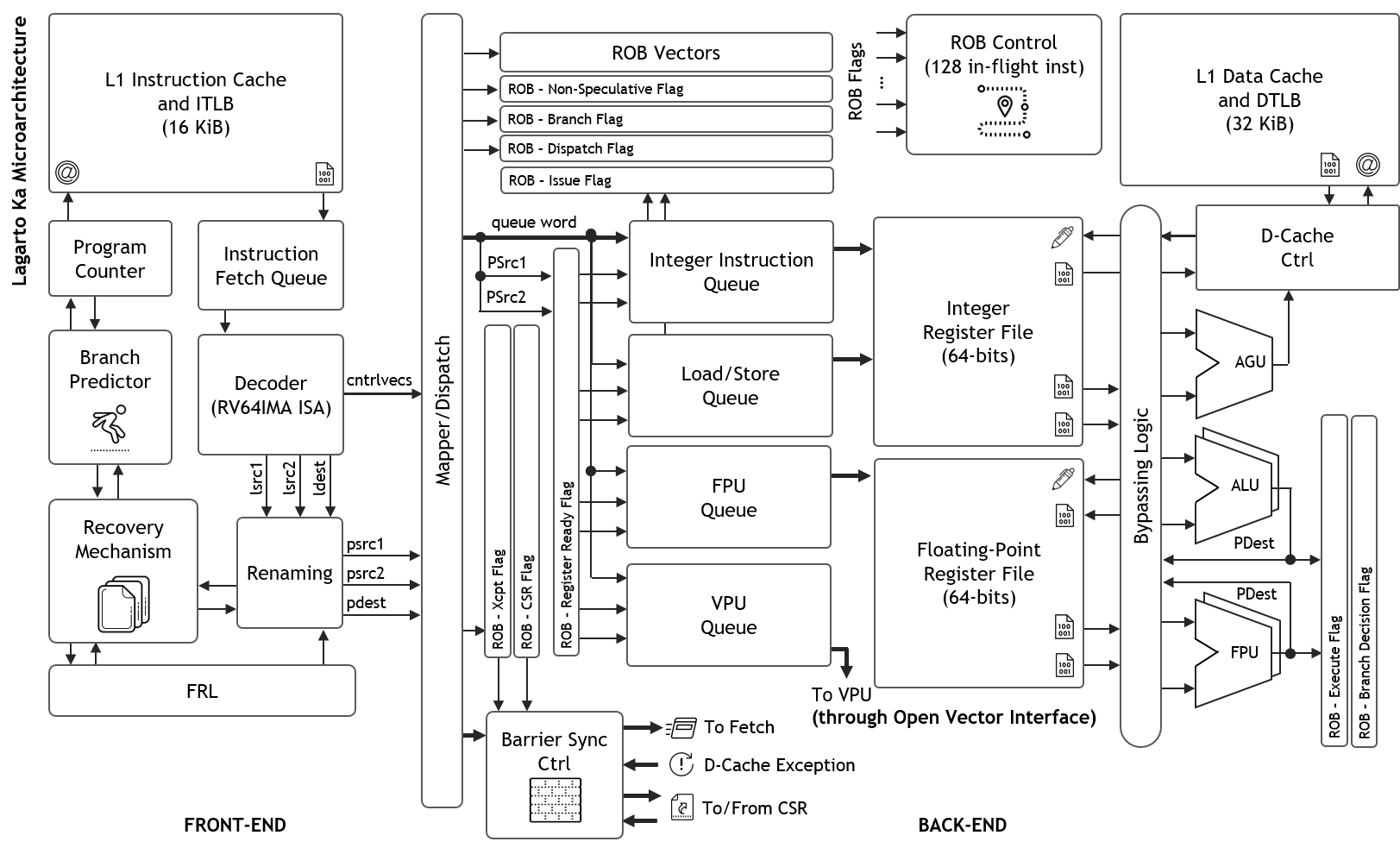

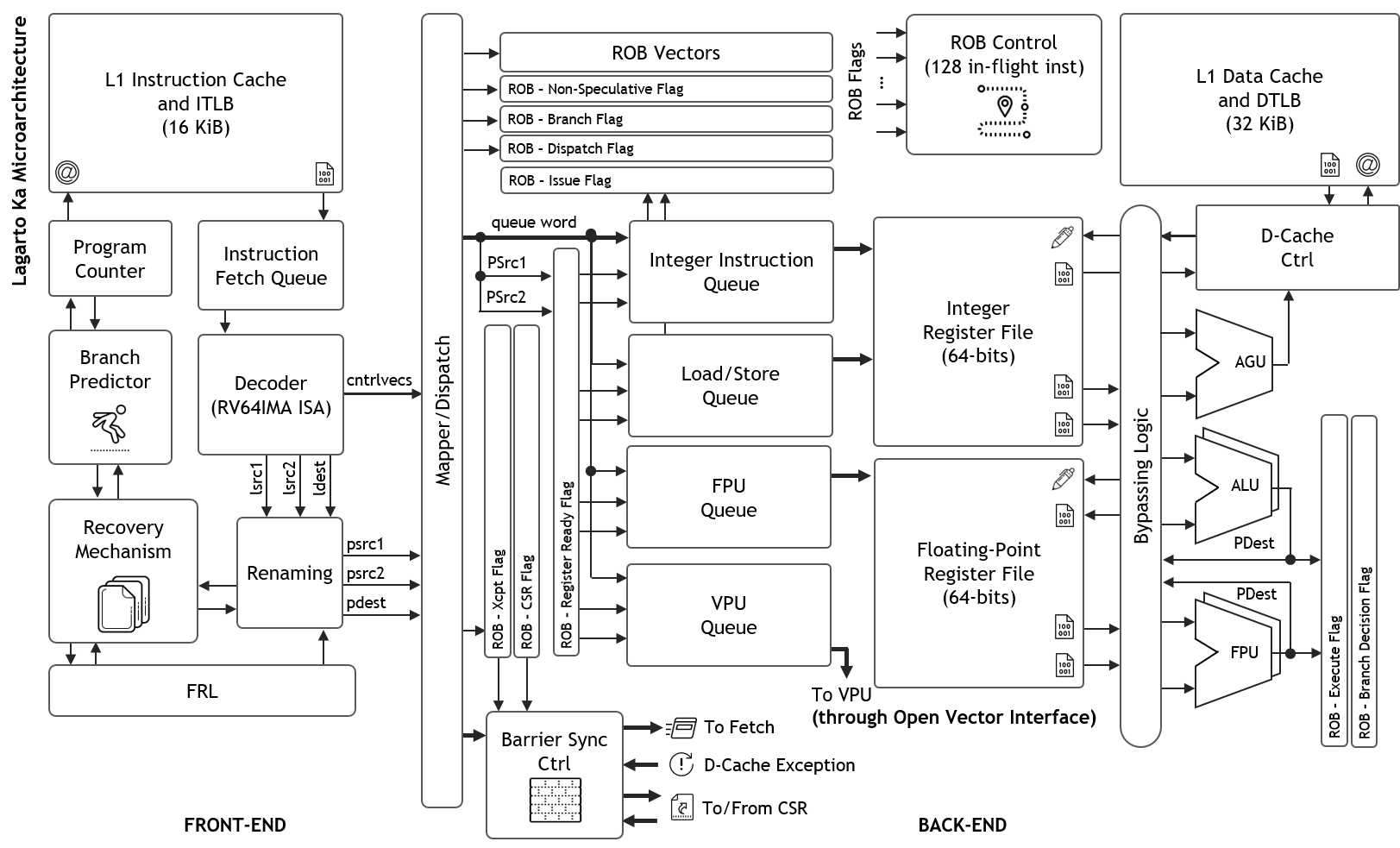

Como se observa en la Figura 1, la microarquitectura del procesador Lagarto Ka se divide en dos bloques fundamentales de procesamiento: el Front-End y el Back-End.

El Front-End es la parte del procesador a cargo de mantener un flujo constante de instrucciones en el pipeline que deben ser traídas desde la memoria caché de instrucciones, decodificadas, y renombradas, para después ser distribuidas en el camino de datos que corresponda a cada instrucción para ser ejecutada correctamente. El renombrado de registros es fundamental en esta etapa del procesamiento ya que con éste se consiguen resolver las falsas dependencias entre instrucciones, manteniendo solo las dependencias verdaderas, lo que permite optimizar la ejecución de instrucciones independientes rompiendo el orden del programa.

Adicionalmente, el Front-End integra un predictor de saltos que permite acelerar la búsqueda de instrucciones al detectar saltos en el código del programa sin la necesidad de haber sido decodificados. Finalmente, es posible restaurar el contexto del procesador a un estado previo ante cualquier fallo gracias a que se cuenta con un mecanismo de recuperación que permite ejecutar de forma efectiva los flujos de instrucciones especulativos.

El segundo bloque de procesamiento, el Back-End, ha sido diseñado para explotar el paralelismo a nivel de instrucción que ofrece el renombrado de registros, adelantando la ejecución de instrucciones tan pronto como sus operandos fuente estén listos, sin importar el orden inicial en el que entran al pipeline. A este proceso se le conoce como ejecución fuera de orden.

La ejecución fuera de orden dentro del procesador Lagarto Ka es controlada gracias a dos estructuras principales: las colas de emisión fuera de orden encargadas de enviar tantas instrucciones como sea posible a las unidades de ejecución cada ciclo de reloj, y el buffer de reordenamiento (ROB), que monitorea el orden del conjunto de instrucciones que se encuentran activas en el Back-End, determina cuándo deben liberarse los recursos hardware una vez que las instrucciones abandonan el pipeline.

Dado que el consumo de energía resulta crítico en el uso de sistemas encastados, el procesador Lagarto Ka integra técnicas de bajo consumo de energía que buscan mitigar este problema.

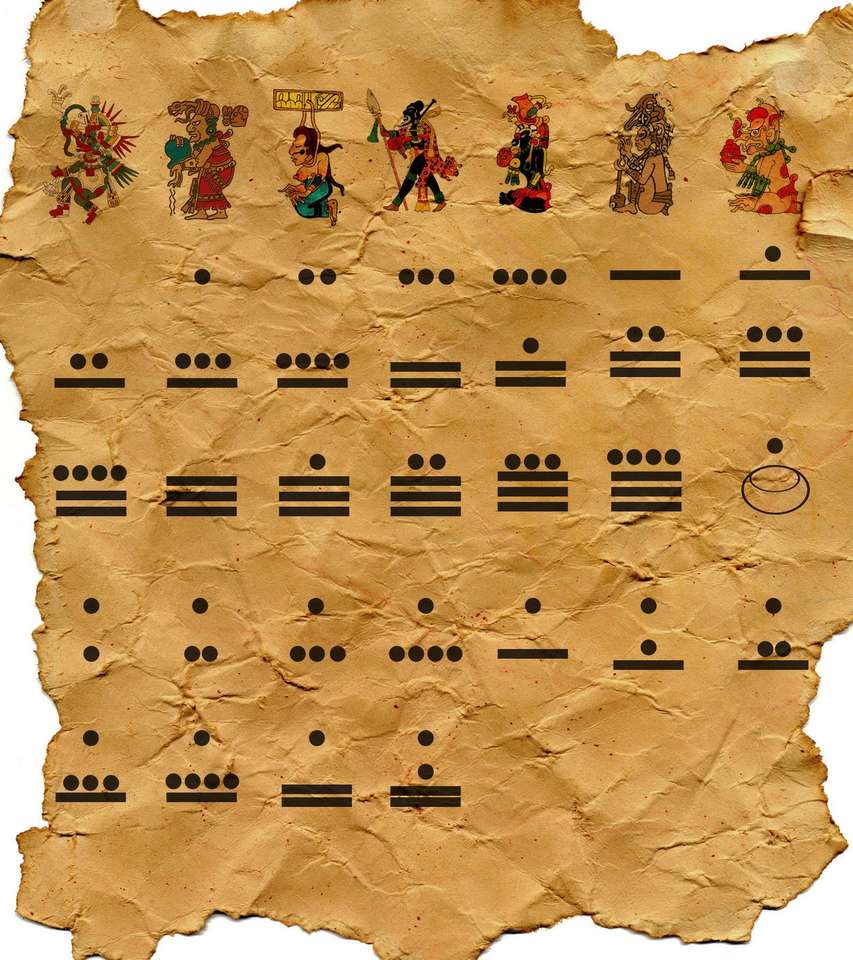

Lagarto Ka es la primera propuesta para alto rendimiento de la familia de procesadores Lagarto. Su nombre está inspirado en la numeración maya con la que también se ha identificado a los primeros diseños fabricados en DRAC. Es así que la primera versión, un procesador escalar en orden que emite una instrucción por ciclo de reloj, ha sido llamada Lagarto Hun, mientras que Lagarto Ka ha sido diseñado para emitir dos instrucciones por ciclo.

Lagarto Ka es el núcleo del chip en el que se integran los distintos aceleradores desarrollados en DRAC, un proyecto que quiere abrir paso a nuevas propuestas de diseño desde la academia dentro del campo de la Arquitectura de Computadoras, inicialmente detonadas por iniciativas de código abierto como la de RISC-V, buscando que en un futuro no muy lejano sea posible aprovechar estas propuestas en productos de uso especializado o doméstico.