Proyecto 1: Diseño e implementación de un procesador fuera de orden

El objetivo principal de esta tarea es diseñar, codificar, verificar y construir el procesador fuera de orden que será el motor de todo el proyecto y donde se le incorporarán los distintos aceleradores que se desarrollarán. El juego de instrucciones elegido es el RISC-V, que es un juego de instrucciones moderno que permite agregar aceleradores al procesador con un juego de instrucciones específico para tal fin. Por otra parte, utilizar RISC-V facilita que nuestro procesador pueda ejecutar programas ya que podemos utilizar las herramientas desarrolladas para RISC-V, desde el sistema operativo hasta los compiladores.

Proyecto 2: Seguridad post-cuántica y técnicas de virtualización

Muchos de los criptosistemas estándar actuales son vulnerables a ataques ejecutados desde ordenadores cuánticos. El NIST americano está intentando encontrar los mejores esquemas criptográficos entre los que no son vulnerables a ataques clásicos y cuánticos. En este proyecto se analizarán diferentes esquemas candidatos y se diseñarán las extensiones seguras para estos esquemas para ser incorporados en el procesador basado en RISC-V. También se desarrollarán e implementarán técnicas de seguridad clásica como la randomización para conseguir tener un procesador fuera de orden seguro y la implementación de los niveles (rings) de seguridad hardware junto con el soporte hardware de los mecanismos de virtualización presentes en el ISA de RISC-V.

Proyecto 3: Arquitecturas de computadores para acelerar aplicaciones de análisis genómico

El objetivo principal de este proyecto es el diseño de nuevas arquitecturas paralelas de alto rendimiento para el procesado y análisis de datos genómicos a gran escala. Estas aplicaciones son un componente muy relevante en las aplicaciones actuales y futuras de la medicina personalizada: la fase de secuenciación es una parte relevante del pipeline de la mayoría de análisis de los datos genómicos y su reducción tiene un impacto directo en el tratamiento de los datos de salud. En este proyecto se estudiarán los requisitos a nivel de arquitectura de estas aplicaciones y se desarrollará un nuevo acelerador basado en un procesador vectorial para este tipo de aplicaciones. Finalmente, se establecerá un ciclo de co-diseño entre los desarrolladores de las aplicaciones de análisis genómico y los diseñadores del acelerador permitiendo una mayor eficiencia y rendimiento.

Proyecto 4: Aceleración de aplicaciones de automoción con computación aproximada en tecnología FDSOI

La llegada de la conducción autónoma requiere del uso de hardware relativamente sencillo (y económico) que dé un rendimiento muy alto dentro de un límite de consumo muy estricto para cumplir con los requerimientos de los sistemas de automoción. Los sistemas de alto rendimiento actuales que podrían dar el rendimiento necesario, lo hacen con un consumo muy alto. En este sentido, y dado que los procesos de conducción autónoma son necesariamente heurísticos y aproximados, este proyecto está enfocado a diseñar un acelerador que, en vez de utilizar hardware determinista para dar resultados aproximados, o unidades aproximadas para implementar operaciones aritméticas deterministas, utilice la computación aproximada para funciones complejas y la tecnología FDSOI (orientada a bajo consumo) que puede introducir alteraciones en los resultados cuando se opera a baja tensión de alimentación, de manera que, sin empeorar la precisión global del proceso de predicción, se puedan implementar sistemas de conducción autónoma con una mejor combinación de rendimiento y consumo, y sin afectar a la requerida fiabilidad. En particular, este proyecto diseñará e implementará la unidad de cálculo que se indica y definirá detalladamente su integración en futuras generaciones del procesador europeo, que ataca los segmentos de supercomputación y automoción.

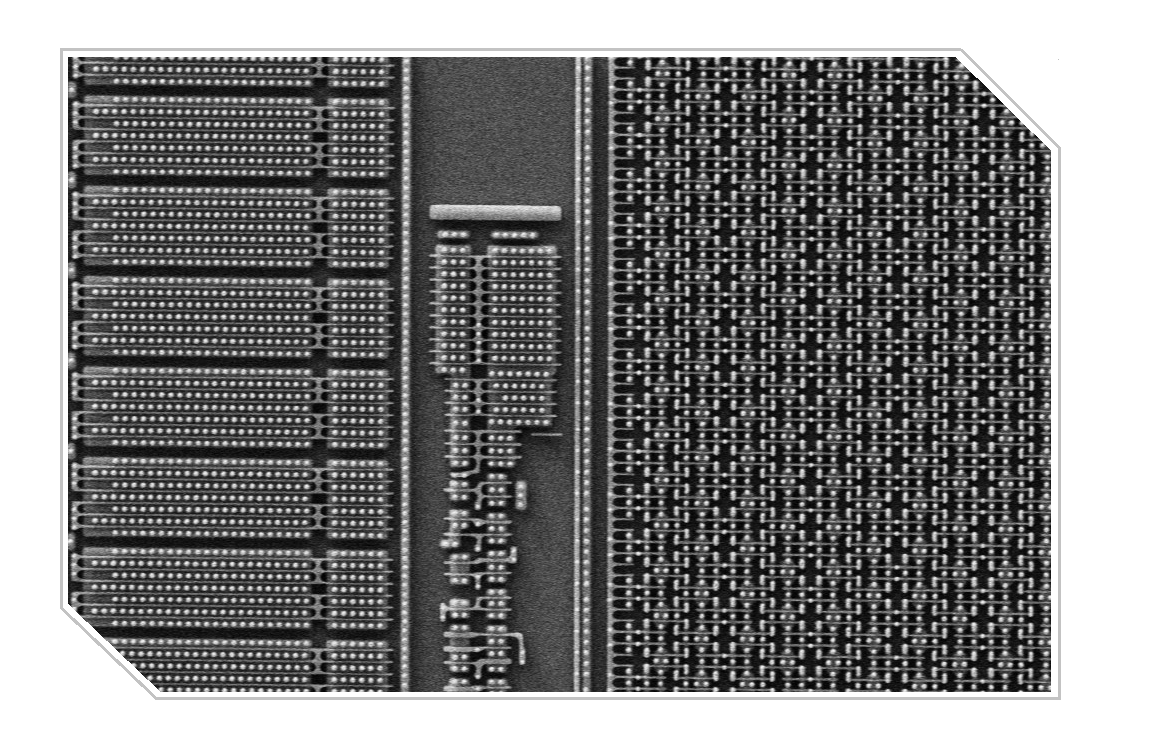

Proyecto 5: Integración, layout y fabricación de prototipos y plataforma de test

En este proyecto se coordinará y gestionará el acceso a las distintas tecnologías desarrolladas en el marco de esta agrupación tecnológica. En particular, se integrarán los distintos bloques necesarios para fabricar el procesador RISC-V y distintos aceleradores diseñados. También se desarrollará la plataforma de testing para poder comprobar que el procesador diseñado funciona correctamente.

Proyecto 6: Difusión y transferencia tecnológica

La comunicación de los resultados de esta agrupación tecnológica, así como la explotación de la IP resultante en forma de contratos de licencia, son claves para el éxito del proyecto. La página web del proyecto incluye la descripción del proyecto y da visibilidad a los resultados del proyecto. Además, se destinará un esfuerzo a difundir la tecnología desarrollada entre todas las universidades de Cataluña mediante la preparación de un kit educacional basado en procesadores RISC-V que podrán usar los estudiantes universitarios de grado, máster y doctorado.