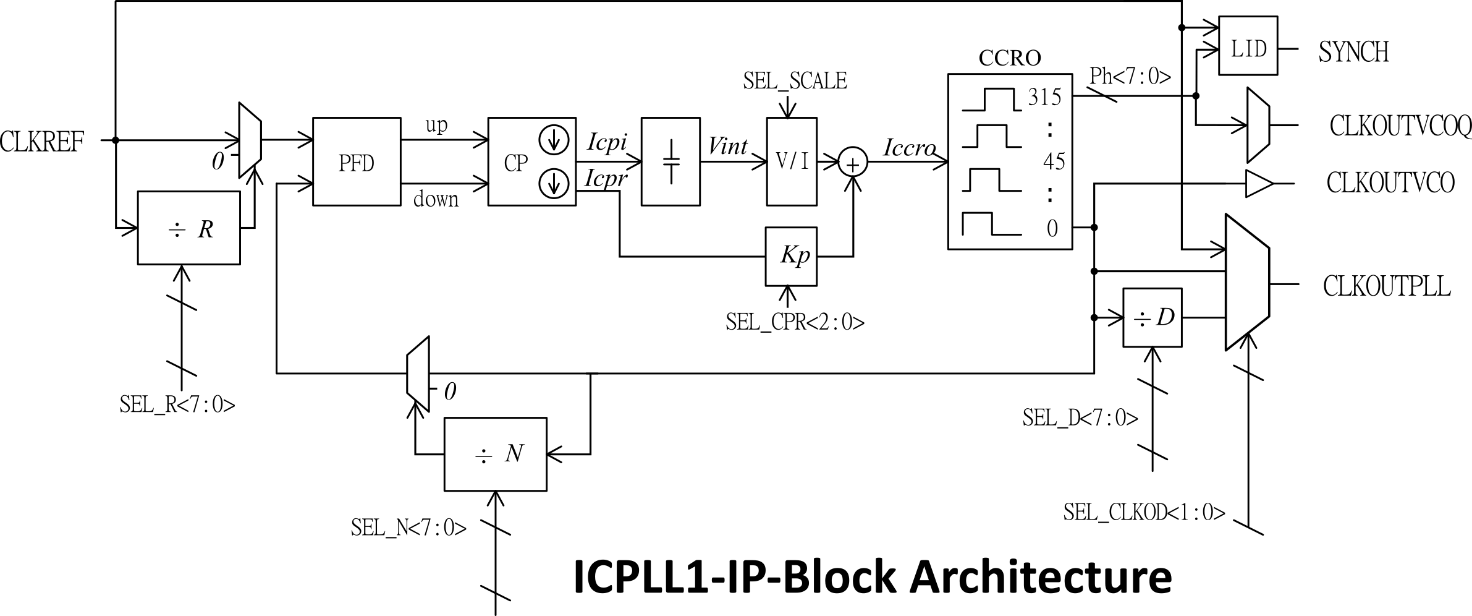

El nuevo procesador DVINO incorpora un generador de reloj interno capaz de suministrar las diferentes frecuencias que marcan el ritmo de funcionamiento del núcleo. La arquitectura del generador es de tipo lazo cerrado con bloqueo de fase (phase-locked loop, PLL), de forma que permite sintetizar frecuencias de reloj elevadas a partir de una única referencia externa de baja frecuencia. En particular, este PLL incluye un oscilador en anillo controlado por corriente y sintonizado mediante un control en tiempo real de fase y frecuencia a fin de que el reloj del núcleo del procesador presente una alta estabilidad junto con un bajo ruido de fase (jitter).

Este PLL ha sido especialmente concebido para:

- Permitir al núcleo trabajar a velocidades hasta seis veces superiores a la frecuencia de referencia externa.

- Compensar las derivas de la frecuencia del reloj debido a la variabilidad tecnológica, a la fluctuación de la alimentación y en las derivas de la temperatura.

- Modificar dinámicamente la frecuencia del núcleo desde el propio programa que esté ejecutando el procesador.

El procesador DVINO se ha diseñado para trabajar a 600 MHz, pero el PLL se ha simulado correctamente por encima de 1.2 GHz. Adicionalmente, la capacidad de cambio dinámico de frecuencia del PLL facilitará al procesador la posibilidad de adaptar, en tiempo real, su velocidad de computación según varios criterios, tales como la carga de trabajo o un consumo objetivo.

Las características principales del PLL integrado dentro del DIVINO son:

- Frecuencia de referencia externa de 200 MHz, opcionalmente divisible a 100 MHz o 50 MHz.

- Frecuencia del reloj del núcleo como múltiplo entero de la frecuencia de referencia en un rango de 400 MHz a 1.2 GHz.

- Posibilidad de proporcionar frecuencias submúltiples del reloj generado por el núcleo.

- Cambio de frecuencia de forma síncrona para evitar funcionamientos inadecuados durante la re-configuración dinámica.

- Tecnología: TSMC CMOS 65nm.

- Alimentación: 1.2 V.

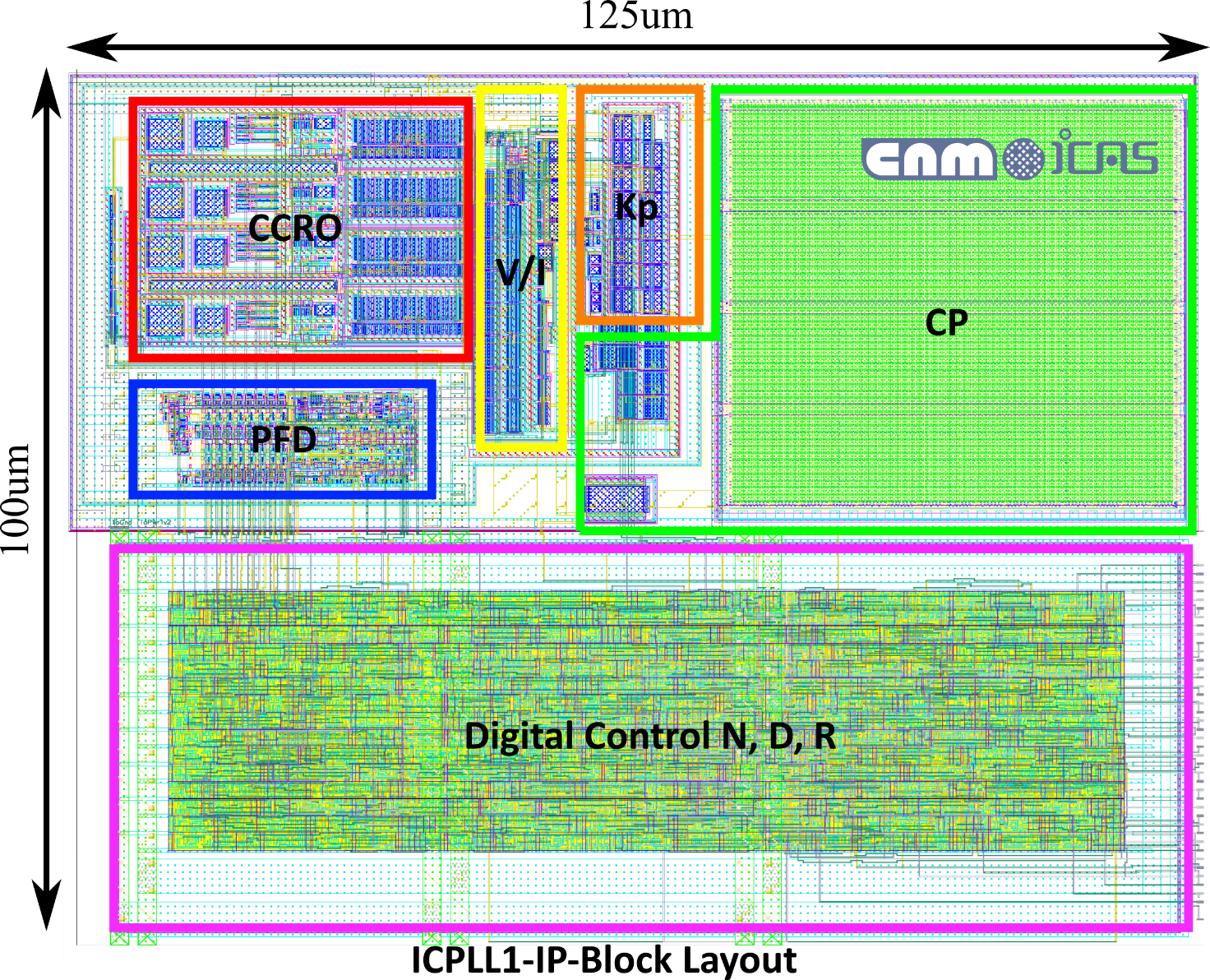

- Área de silicio del bloque IP: 0.0125 mm².