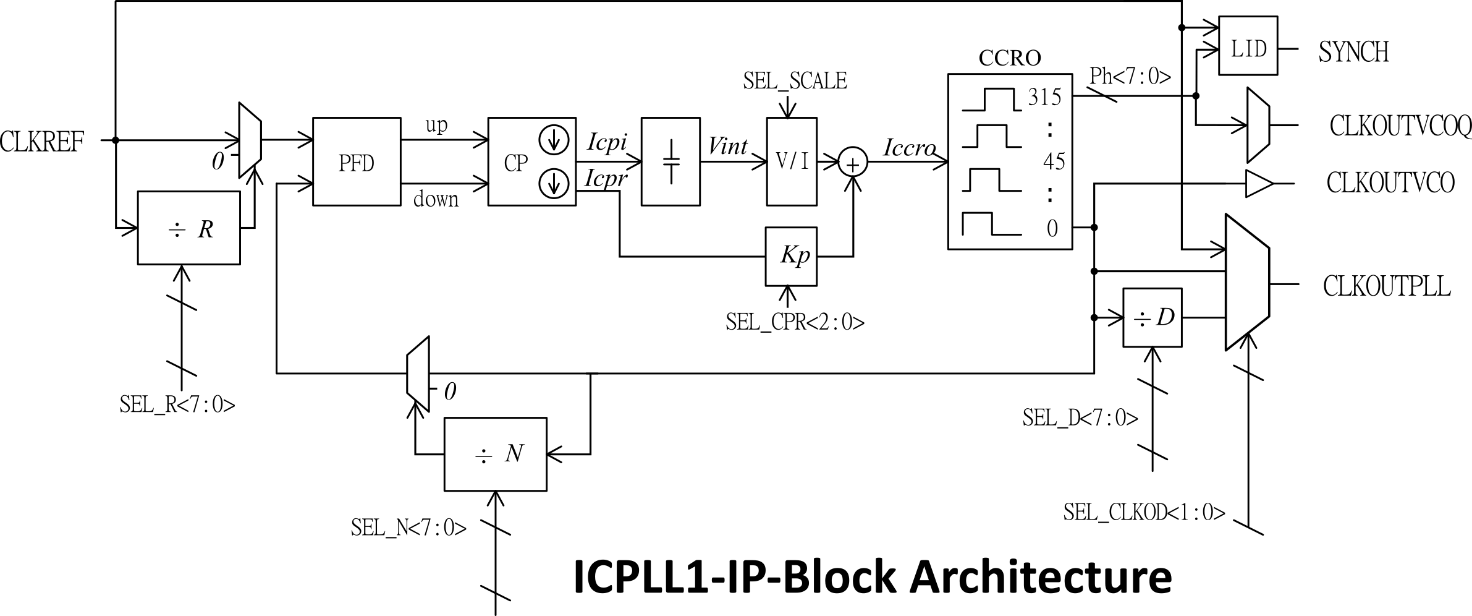

El nou processador DVINO incorpora un generador de rellotge intern capaç de subministrar les diferents freqüències que marquen el ritme de funcionament del nucli. L’arquitectura del generador és de tipus llaç tancat amb bloqueig de fase (phase-locked loop, PLL), de manera que permet sintetitzar freqüències de rellotge elevades a partir d’una única referència externa de baixa freqüència. En particular, aquest PLL inclou un oscil·lador en anell controlat per corrent i sintonitzat mitjançant un control en temps real de fase i freqüència a fi i efecte que el rellotge del nucli del processador presenti una alta estabilitat junt amb un baix soroll de fase (jitter).

Aquest PLL ha estat especialment concebut per:

- Permetre al nucli treballar a velocitats fins a sis cops superiors a la freqüència de referència externa.

- Compensar les derives de la freqüència del rellotge degut a la variabilitat tecnològica, a la fluctuació de l’alimentació i a les derives de la temperatura.

- Modificar dinàmicament la freqüència del nucli des del propi programa que estigui executant el processador.

El processador DVINO s’ha dissenyat per treballar a 600 MHz, però el PLL s’ha simulat correctament per sobre de 1.2 GHz. Addicionalment, la capacitat de canvi dinàmic de freqüència del PLL facilitarà al processador la possibilitat d’adaptar, en temps real, la seva velocitat de computació segons varis criteris, como ara la càrrega de treball o un consum objectiu.

Les característiques principals del PLL integrat dins el DIVINO són:

- Freqüència de referencia externa de 200 MHz, opcionalment divisible a 100 MHz o 50 MHz.

- Freqüència del rellotge del nucli com a múltiple sencer de la freqüència de referència en un rang de 400 MHz a 1.2 GHz.

- Possibilitat de proporcionar freqüències submúltiples del rellotge generat per all nucli.

- Canvi de freqüència de forma síncrona per evitar funcionaments inadequats durant la re-configuració dinàmica.

- Tecnologia: TSMC CMOS 65nm.

- Alimentació: 1.2 V.

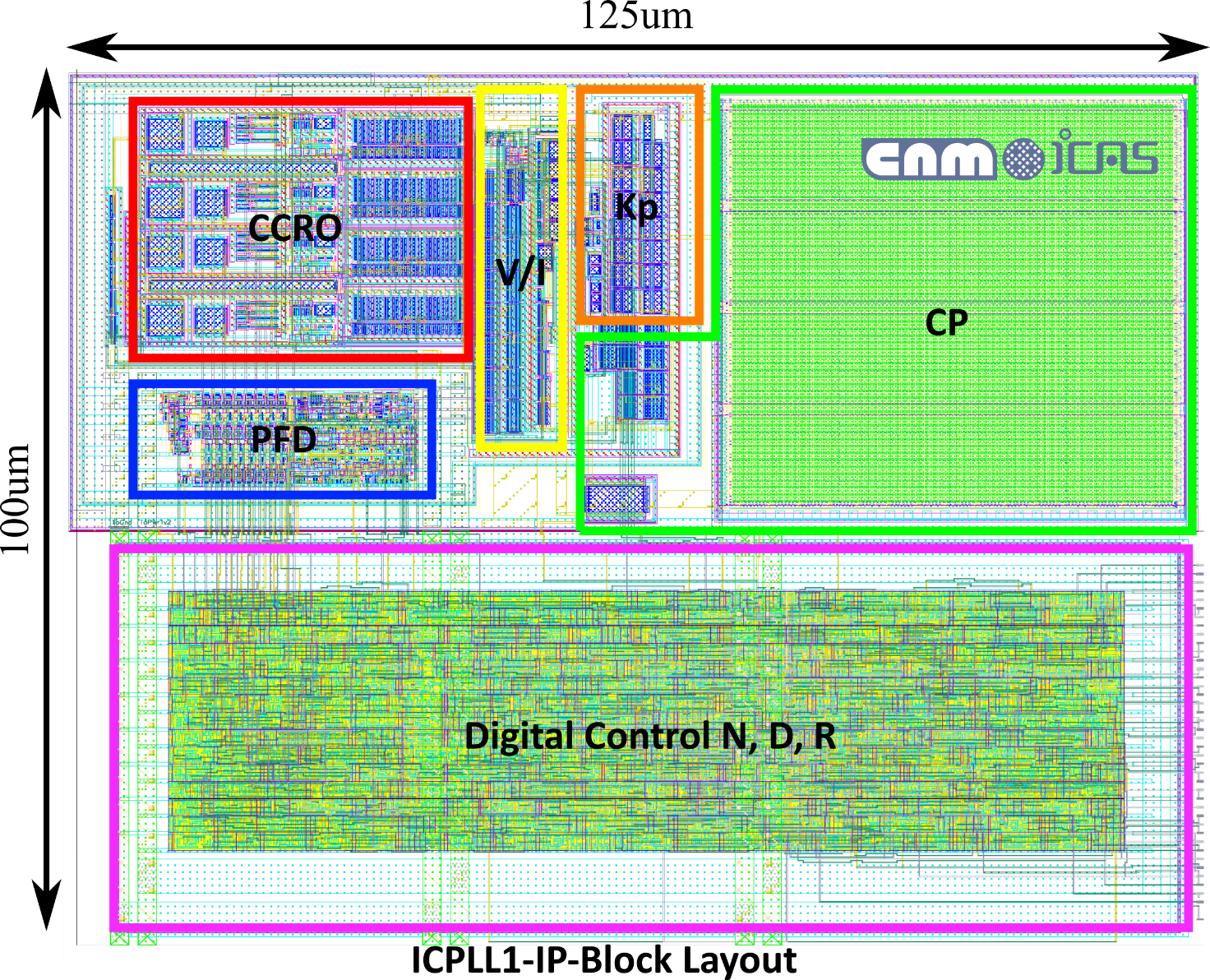

- Àrea de silici de bloc IP: 0.0125 mm².