David Castells-Rufas, Santiago Marco-Sola, Juan Carlos Moure, Quim Aguado, Antonio Espinosa

Los filtros de pre-alineamiento proponen métodos útiles para reducir los requerimientos computacionales de las aplicaciones de mapeo de secuencias genómicas.

La mayoría de los filtros están basados en estimaciones o cálculos de la distancia de edición entre las secuencias cortas de entrada y las localizaciones candidatas en el genoma de referencia. Se suele usar un subconjunto de los elementos de la tabla obtenida mediante programación dinámica al computar la distancia de Levenshtein entre las secuencias cortas y la referencia.

Algunas implementaciones FPGA de estos filtros pre-alineamiento utilizan herramientas clásicas HDL (Hardware Description Language) que limitan su portabilidad. Actualmente, las herramientas HLS (High Level Synthesis) para C/C++ pueden ser usadas en la mayoría de aceleradoras computacionales FPGA disponibles en los proveedores de sistemas de computación en la nube. Nuestro trabajo ha consistido en reimplementar y optimizar varios filtros del estado del arte utilizando herramientas HLS basadas en C/C++ para expandir su portabilidad a un amplio rango de sistemas que permiten ejecutar el runtime OpenCL.

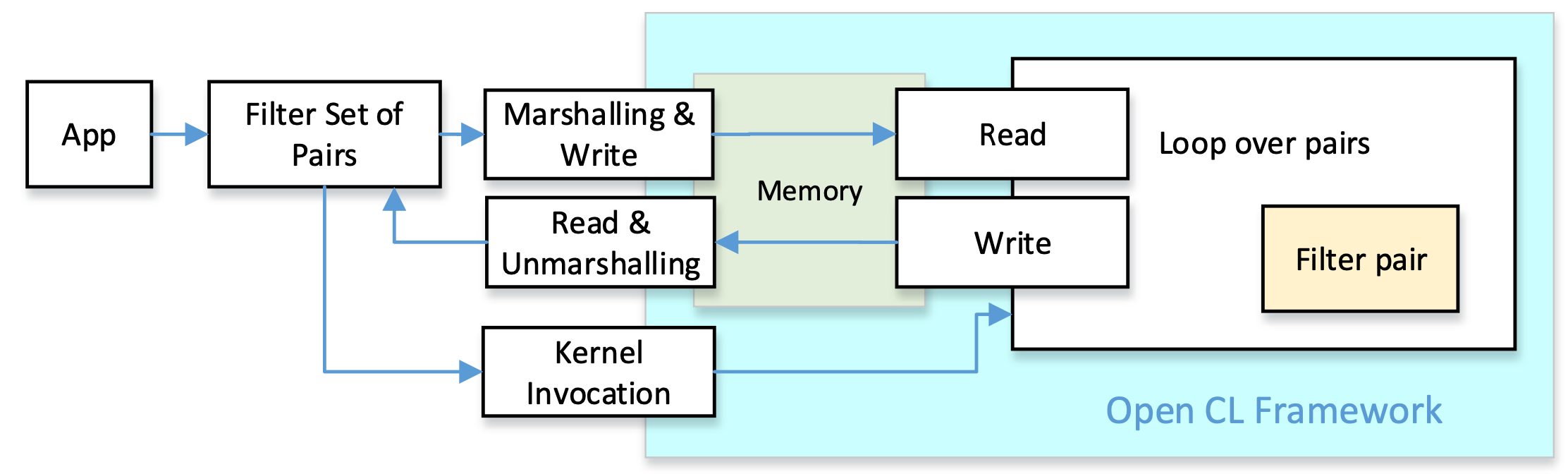

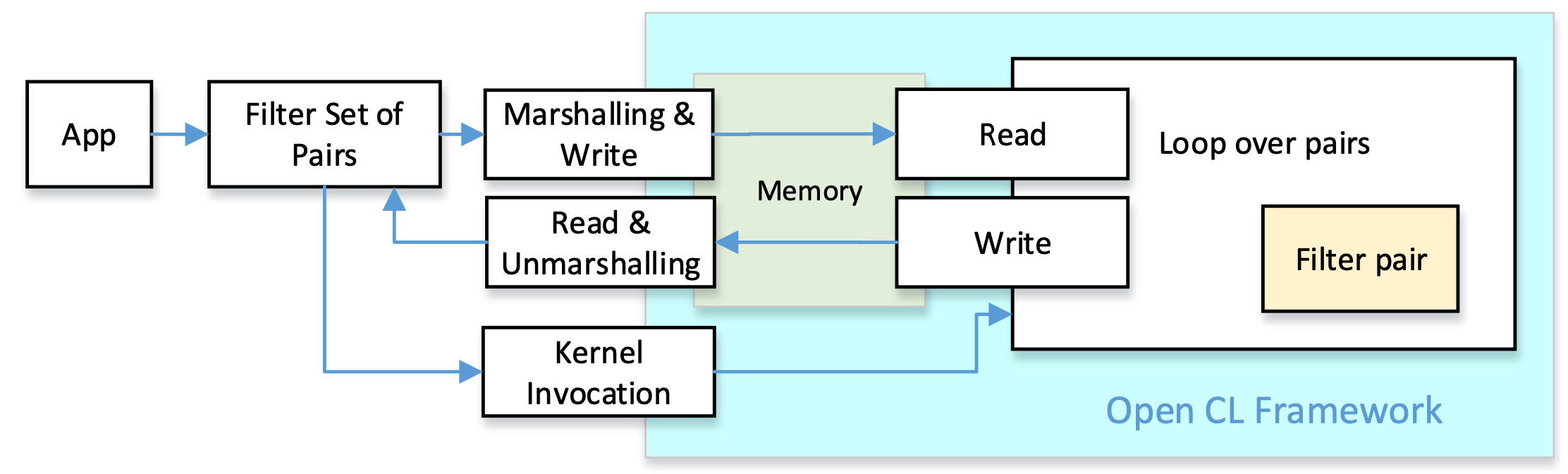

Nuestro objetivo es crear filtros pre-alineamiento que puedan ser integrados en centros de datos equipados con aceleradores FPGA de forma simple. Hemos seleccionado OpenCL como el entorno de implementación FPGA con mayor disponibilidad en las plataformas existentes. Todos los filtros estudiados comparten el mismo objetivo: comparar un patrón con un texto para obtener una estimación de la distancia entre ambos. Este proceso se implementa en C/C++ con funciones que contienen el mismo número de parámetros y retornan el mismo tipo de valores. Podemos usar esta encapsulación para implementar un conjunto común de funciones para todos los filtros tanto en el servidor como en el acelerador como se muestra en el esquema lógico:

El análisis algorítmico que permite traducir las propuestas existentes de HDL a HLS basado en C/C++ tiene como objetivo simplificar los métodos y generar oportunidades para la optimización. La combinación de estos dos aspectos ha de obtener un mejor rendimiento reduciendo el uso de recursos.