El procesador Sargantana contará con soporte hardware para entornos virtualizados, cumpliendo la especificación de RISC-V Privileged Architecture [1]. Esto permite que entornos virtualizados, como máquinas virtuales, se ejecuten de forma más eficiente.

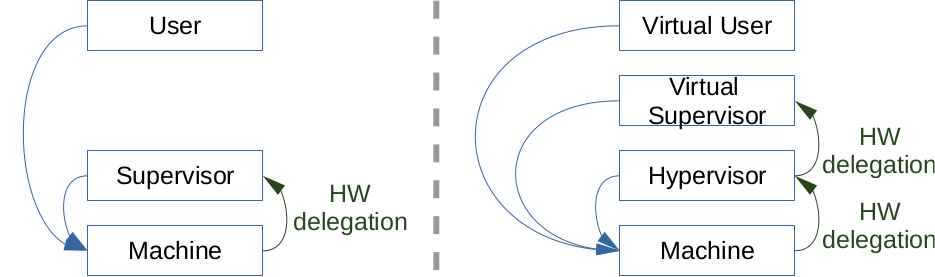

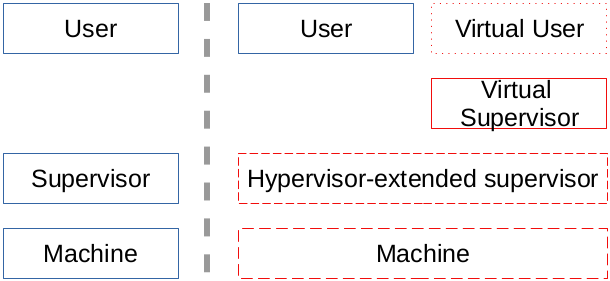

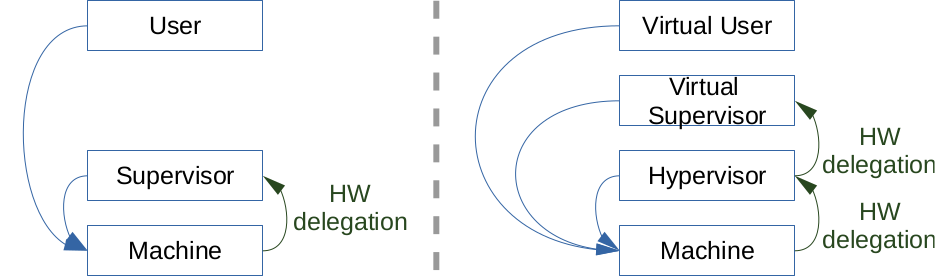

A efectos prácticos, significa que se añade un nuevo modo de ejecución (hipervisor) que virtualiza los modos de ejecución habituales (usuario-virtual y supervisor-virtual). Para añadir este soporte al procesador Sargantana, deben modificarse ciertas partes del núcleo, en particular:

Conjunto de registros hardware El núcleo ya dispone de registros de control y estado (CSRs) para rastrear y controlar los modos de ejecución habituales (usuario, supervisor y máquina). La nueva extensión requiere modificar algunos de estos registros para activar la virtualización, así como añadir nuevos CSRs para el nuevo modo (hipervisor) y para los modos virtualizados (usuario-virtual y supervisor-virtual).

Gestión de las interrupciones y excepciones Por defecto, todas las interrupciones y excepciones son tratadas por el modo máquina, que puede realizar el tratamiento o invocar a una rutina del nivel superior. Dado que este tratamiento puede ser lento, se dispone de un mecanismo hardware que permite delegar el tratamiento en un nivel superior (evitando los saltos intermedios). Con el nuevo modo hipervisor, es necesario añadir un nuevo nivel de delegación y añadir todo un conjunto de nuevas excepciones propias de los entornos virtualizados.

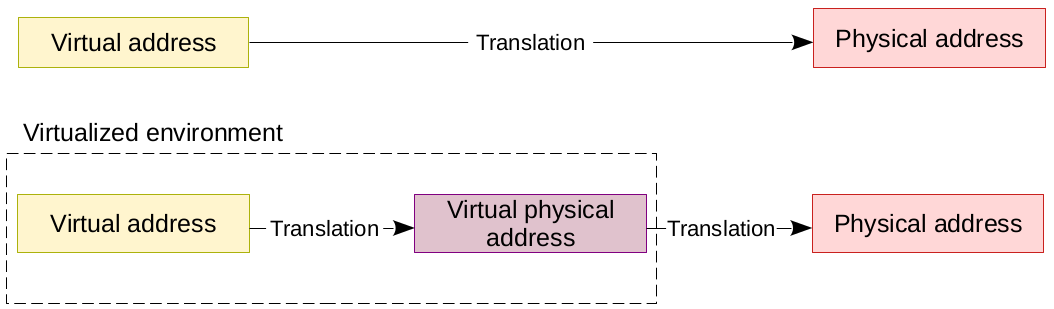

Gestión del espacio de direcciones Hay que añadir soporte para entornos virtualizados en el módulo que se encarga de proteger y traducir las direcciones virtuales a direcciones físicas. En estos entornos todas las direcciones físicas están virtualizadas y, por lo tanto, hay que hacer dos traducciones: 1) para traducir una dirección virtual a una dirección física dentro el entorno virtualizado (física virtual) y 2) para traducir esta física virtual y obtener la dirección física real dentro de la máquina. Es necesario tener presente que esta segunda fase de traducción no sólo afecta a la dirección física virtual resultado de la primera fase, sino a todas las estructuras intermedias (tablas de páginas) usadas en la propia traducción.

Nuevas instrucciones La especificación del hipervisor también incluye nuevas instrucciones para gestionar la memoria de los entornos virtualizados.

Aparte de las modificaciones del procesador, también se deben realizar nuevos programas de prueba que tengan en cuenta la verificación de estos entornos virtualizados y que las modificaciones implementadas no afecten al funcionamiento normal del procesador en entornos no virtualizados.

Referencias

[1] RISC-V Fundation. RISC-V Privileged Architecture, version 20210915-Public-Review-draftn, https://github.com/riscv/riscv-isa-manual/releases/tag/riscv-privileged-20210915-public-review