Project 1: Design and implementation of an out-of-order processor

The main goal of this task is to design, code, verify and build the out-of-order processor that will be the motor of the project. Different accelerators will be developed and incorporated into the processor. In order to do so, the project will use RISC-V, a modern set of instructions which allows the addition of accelerators to a processor with a specific set of instructions. On the other hand, RISC-V facilitates the execution of programs by our processor because it provides tools developed by RISC-V, from the operating system to the compilers.

Project 2: Post-quantum security and virtualization techniques

Many standard cryptosystem nowadays are vulnerable to quantum computing attacks. The American NIST is trying to find the best cryptographic schemes among the ones that are resistant to classic and quantum attacks. This project will analyse different candidate schemes and design secure extensions for those schemes that will be incorporated into the RISC-V-based processor. Classic security techniques, such as randomization to achieve a secure out-of-order processor and the implementation of protection rings together with the support hardware of the virtualisation mechanisms in the RISC-V ISA.

Project 3: Computer architecture to accelerate genomic analysis applications

The main goal of this project is to design new high-performance parallel architectures for the large-scale processing and analysis of genomic data. These applications are a very relevant component in the current and future applications of personalized medicine: sequencing is an important phase of the pipeline of most of genomic data analysis and its reduction has a direct impact in the treatment of health data. This project will study the architecture requirements of these applications and develop a new accelerator based on the vectorial processor for these kind of applications. Finally, a new co-design cycle will be established between the developers of genomic analysis applications and the designers of the accelerator. This will allow a higher efficiency and performance.

Project 4: Acceleration of automotive applications with approximate computing in FDSOI technology

The arrival of self-driving cars requires the use of relatively simple (and affordable) hardware for a very high performance within a very strict limit of consumption in order to meet the requirements of automotive systems. Current high-performance systems able to provide the required performance have a very high consumption. In this sense, and since the self-driving processes are necessarily heuristic and approximate, this project will focus on the design of an accelerator that, instead of using deterministic hardware to give approximate results or approximate units to implement arithmetic deterministic operations, uses approximate computing for complex functions and FDSOI (Fully Depleted Silicon On Insulator) technology. This technology focuses on energy-efficiency and is able to introduce alterations in the results when operating in low voltage. In this way, it is possible to implement self-driving systems with a better combination of performance and consumption without making the global precision of the prediction process worse and without affecting the required reliability. In particular, this project will design and implement the indicated computing unit. It will also carefully define its integration in future generations of the European processor, which deals with the supercomputing and self-driving segments.

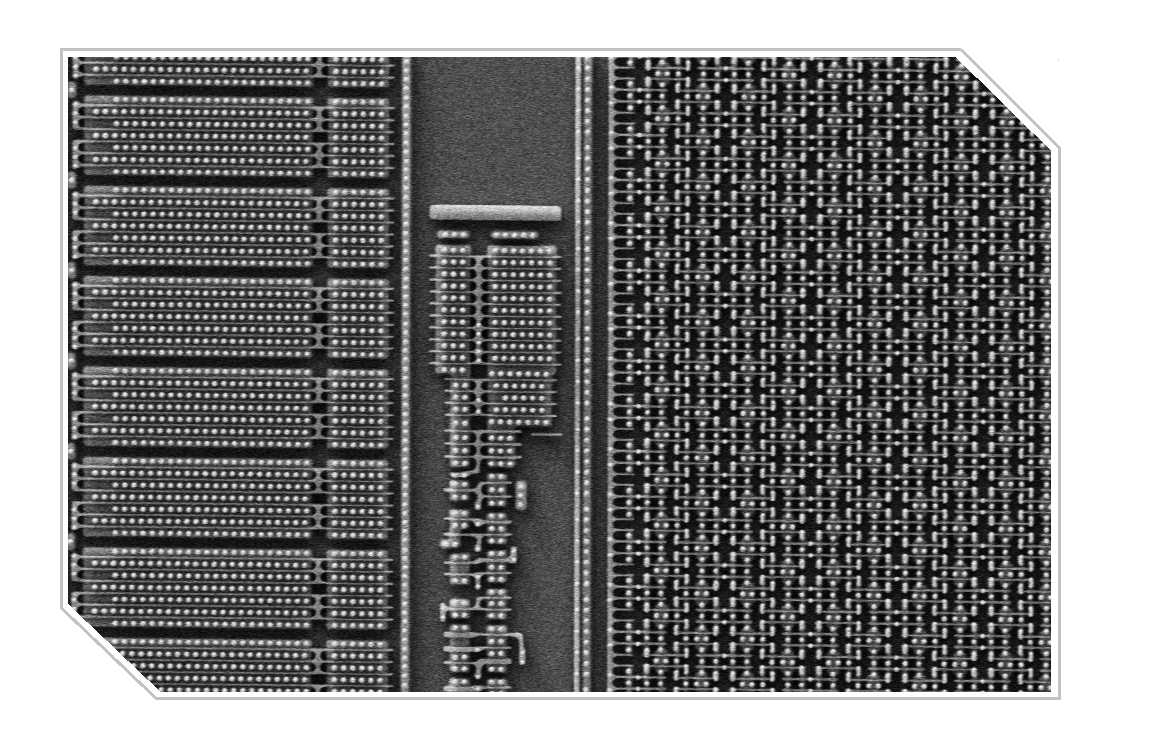

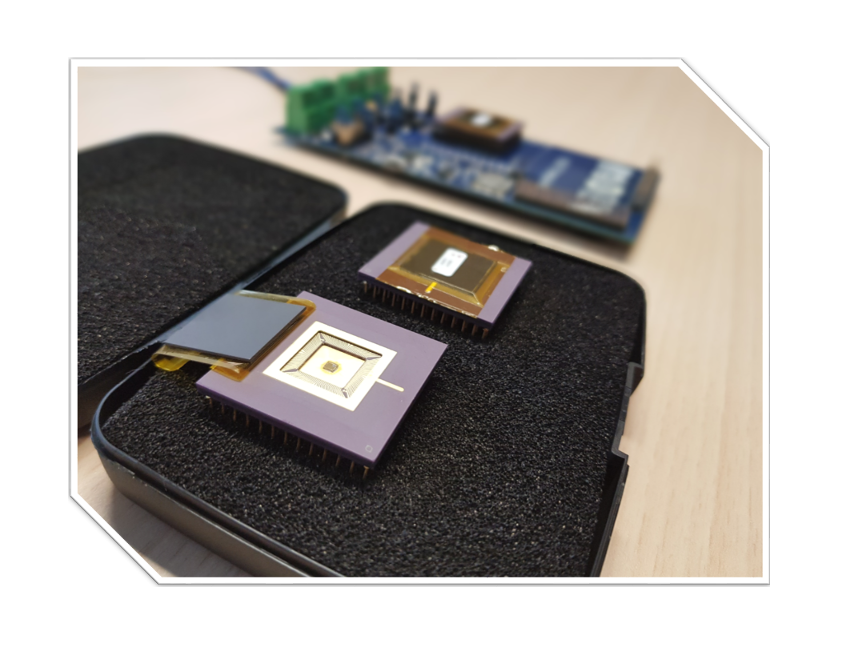

Project 5: Integration, layout and fabrication of prototypes and test platform

and fabrication of prototypes and test platform

This project will coordinate and manage the access to the different technologies developed in this consortium's framework. In particular, the different blocks needed to build a RISC-V processor will be integrated and the different accelerators will be designed. The testing platform to test the designed processor's performance will also be developed.

Project 6: Dissemination and technology transfer

The communication of the project's results, as well as the exploitation of the resulting IP in the form of licensing contracts, are key for the success of the project. The website includes a description of the project and displays the results of the project. Constant efforts will be devoted to disseminate the technologies developed among all the universities in Catalonia by means of the preparation of an educational kit based on RISC-V processors to be used by undergraduate and postgraduate university students.