The Microelectronics design and prototype testing group from the Electronic and Biomedical Engineering Department of the University of Barcelona (UB) is leading the integration, layout and prototype (tape-out) fabrication of the DRAC processors, as well as developing the tests platforms for such processors. DRAC is a research project with the aim to produce RISC-V processors and different accelerators trying to achieve the maximum possible performance while minimizing power consumption. To accomplish that, a correct selection of the technological process where the processors will be fabricated is mandatory, as it affects performance, power consumption and fabrication costs. In the DRAC project several technologies have been studied, but the selected one is the 22 nm FDSOI (22FDX) technological process from Globalfoundries (GF), as it allows us to target clock frequencies above 1GHz, it gives us different options to reduce power consumption and the fabrication costs are relatively low.

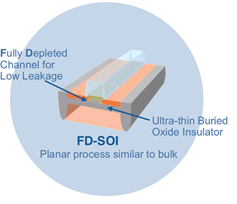

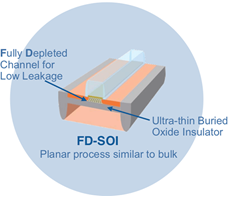

Figure 1: Schematic view of a transistor in 22 nm FD-SOI technology from GF. Image taken from link (Dec. 15th 2020)

GF is an American semiconductor foundry based in Santa Clara, California, United States. GF has five 200 mm wafer manufacturing plants in Singapore, a 300 mm plant each in Germany and Singapore, and three plants in the United States - a 200 mm plant in Vermont (where it is the largest private employer) and two 300 mm plants in New York. However, the foundry in which the 22 nm process is developed is located in Dresden, Germany.

The 22FDX process offers the best combination of performance, power consumption and cost for Internet of Things (IoT) devices, conventional mobile telephony, RF connectivity, networks, etc. The "22FDX™" platform offers FinFET-like performance and energy efficiency at a cost comparable to flat 28nm technologies, providing an optimal solution for the aforementioned markets. 22DFX is an existing process since 2015. Therefore, it is sufficiently stable and mature.

This process provides great flexibility in the power / speed binomial thanks to the control of the substrate voltage, which will be positive (Fordward Body Bias - FBB) for devices in which it is desired to increase efficiency and negative (Reverse Body Bias - RBB) to reduce consumption by leaks. The 22FDX process also offers transistors with different threshold voltages to increase these possibilities. Thus, as it is common in sub-micron processes, transistors with low threshold voltage (SLVT / LVT), medium threshold voltage (RVT / HVT) and high threshold voltage (ULL) are available.