El grup de disseny de microelectrònica i test de prototips del Departament d’Enginyeria Electrònica i Biomèdica de la Universitat de Barcelona (UB) lidera la integració, layout i fabricació de prototipus (tape-out) dels processadors DRAC, a més de desenvolupar les plataformes de test per a aquests processadors. DRAC és un projecte d’investigació amb l’objectiu de produir processadors RISC-V i diferents acceleradors que intenten aconseguir el màxim rendiment possible tot minimitzant el consum d’energia. Per aconseguir-ho, és obligatòria una selecció correcta del procés tecnològic on es fabricaran els processadors, ja que afecta el rendiment, el consum d’energia i els costos de fabricació. En el projecte DRAC s’han estudiat diverses tecnologies, però la seleccionada és el procés tecnològic FD-SOI (22FDX) de 22 nm de Globalfoundries (GF), ja que ens permet arribar a freqüències de rellotge superiors a 1 GHz, ens dona diferents opcions per reduir el consum d'energia i els costos de fabricació són relativament baixos.

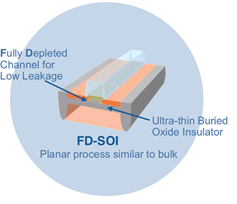

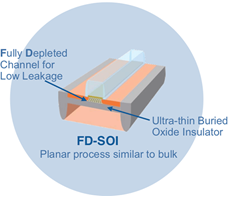

Figura 1: Vista esquemàtica d’un transistor en la tecnologia de 22 nm FD-SOI de GF. Imatge extreta de link (15/Dec/2020)

GF és una planta de fabricació de semiconductors (de l’anglès foundry) nord-americana amb seu a Santa Clara, Califòrnia, Estats Units. GF té cinc plantes de fabricació d’oblees de 200 mm a Singapur, dues plantes de 300 mm a Alemanya i a Singapur i tres plantes més als Estats Units: una planta de 200 mm a Vermont (on és l’ocupador privat més gran) i dues plantes de 300 mm a Nova York. Tot i això, la planta de fabricació de semiconductors on es desenvolupa el procés de 22 nm es troba a Dresden, Alemanya.

El procés 22FDX ofereix la millor combinació de rendiment, consum d'energia i cost per a dispositius Internet de les coses (IoT), telefonia mòbil convencional, connectivitat RF, xarxes, etc. La plataforma "22FDX ™" ofereix un rendiment similar a FinFET i eficiència energètica a un cost comparable a les tecnologies planars de 28 nm, proporcionant una solució òptima per als mercats esmentats. 22DFX és un procés existent des del 2015. Per tant, és prou estable i madur.

Aquest procés proporciona una gran flexibilitat en el binomi potència / velocitat gràcies al control de la tensió del substrat, que serà positiu (Fordward Body Bias - FBB) per als dispositius en els quals es desitgi augmentar l’eficiència i el negatiu (Reverse Body Bias - RBB) per reduir el consum per fuites. El procés 22FDX també ofereix transistors amb voltatges de llindar diferents per augmentar aquestes possibilitats. Per tant, com és habitual en processos sub-micrònics, hi ha disponibles transistors amb voltatge de llindar baix (SLVT / LVT), voltatge de llindar mitjà (RVT / HVT) i voltatge de llindar alt (ULL).

Els processadors DRAC tenen com a objectiu augmentar el rendiment (és a dir, es dirigiran a freqüències de rellotge superiors a 1 GHz), la qual cosa significa que s’utilitzaran transistors de baix voltatge llindar (SLVT / LVT) i FBB per al processador, memòries SRAM i alguns blocs analògics com el PLL . Tot i això, sempre és imprescindible aconseguir un consum d’energia molt baix, per tant, també s’implementaran tècniques de baix consum com “clock gating”, escalat dinàmic de voltatge i freqüència (DVFS) i la reducció de la tensió de polarització del substrat (polarització zero). A més, qualsevol bloc / circuit addicional sense restriccions de velocitat agressives utilitzaria transistors de voltatge llindar mitjà (RVT / HVT).

Els prototips (tape-outs) es fabricaran a través del consorci Europractice mitjançant els serveis Multi-Project-Wafer (MPW). El primer prototip estarà disponible a finals de 2021, mentre que el segon prototip estarà disponible a finals de 2022.