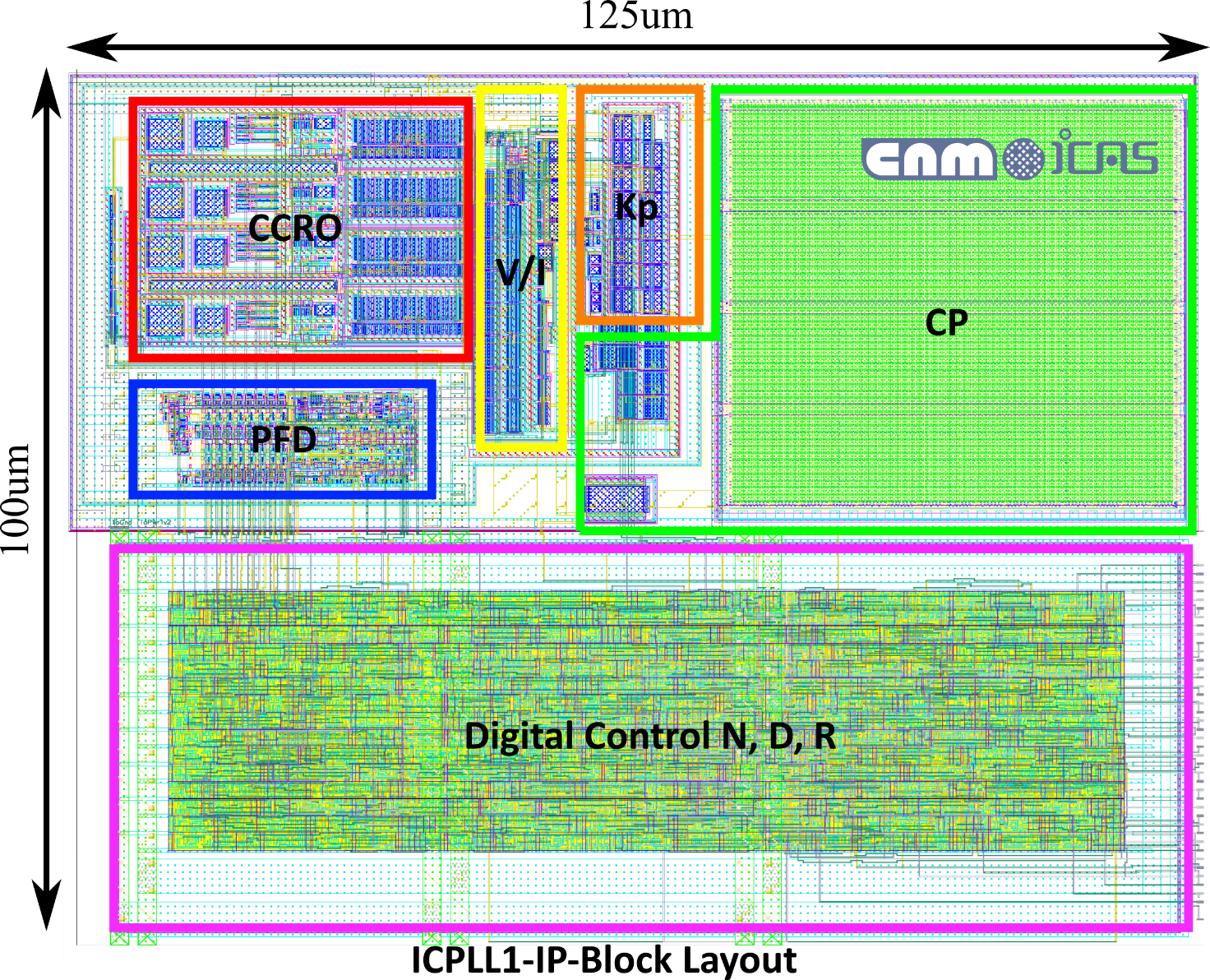

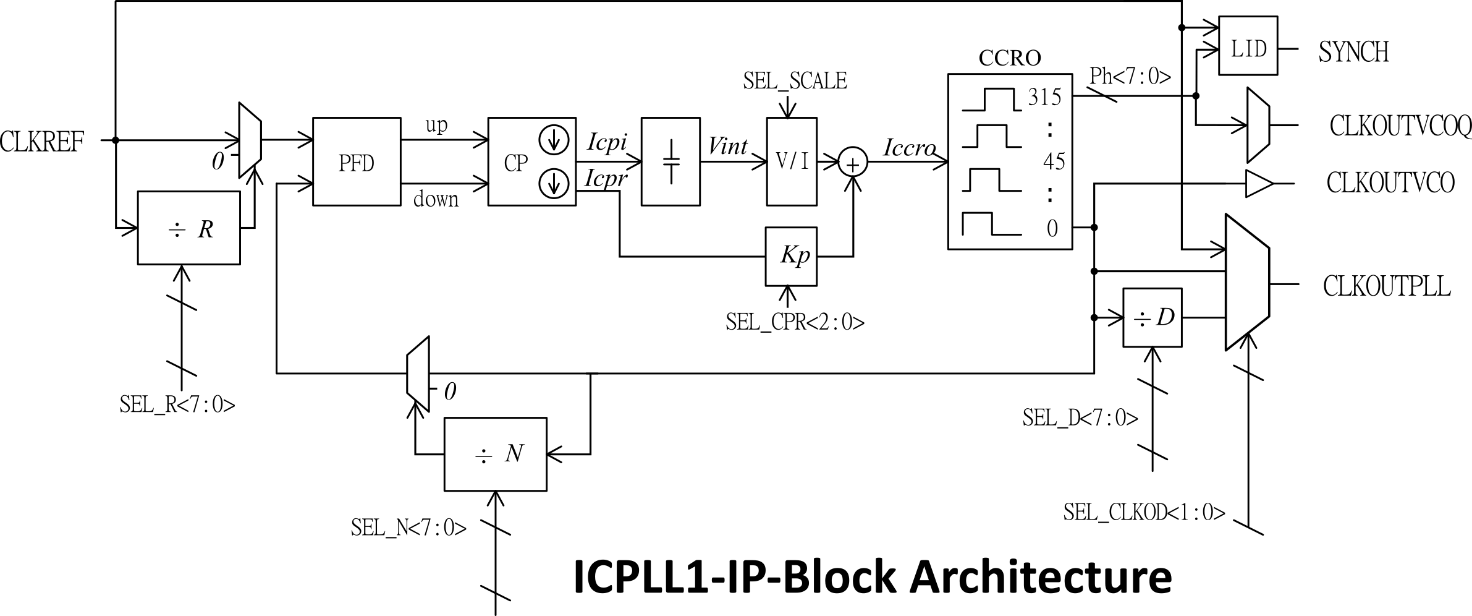

The new DVINO processor incorporates an internal clock generator capable of supplying the different frequencies that mark the operating rhythm of the core. The generator architecture is phase-locked loop (PLL), so it allows high clock frequencies to be synthesized from a single low-frequency external reference. In particular, this PLL includes a ring oscillator controlled by current and tuned by a real-time control of phase and frequency so that the processor core clock has high stability along with low phase noise (jitter).

This PLL has been specially designed for:

- Allow the core to work at speeds up to six times higher than the external reference frequency.

- Compensate for drifting of the clock frequency due to technological variability, power fluctuation and temperature drift.

- Dynamically modify the kernel frequency from the program itself that is running the processor.

The DVINO processor has been designed to work at 600 MHz, but the PLL has been successfully simulated above 1.2 GHz. In addition, the PLL's dynamic frequency change capability will make it easier for the processor to adjust its computing speed in real time according to various criteria, such as workload or target consumption.

The main characteristics of the PLL integrated within the DIVINO are:

- External reference frequency of 200 MHz, optionally divisible by 100 MHz or 50 MHz.

- Kernel clock frequency as an integer multiple of the reference frequency in a range of 400 MHz to 1.2 GHz.

- Possibility to provide submultiple frequencies of the clock generated for the core.

- Frequency change synchronously to prevent improper operation during dynamic reconfiguration.

- Technology: TSMC CMOS 65nm.

- Power supply: 1.2 V.

- Silicon area of the block IP: 0.0125 mm².