Avances recientes en computación cuántica auguran la llegada de ordenadores cuánticos eficientes en un futuro próximo. Aunque muchas aplicaciones se podrían beneficiar de dichos avances, este nuevo paradigma computacional puede suponer una amenaza para la seguridad de las tecnologías de la comunicación, y provocar el colapso de buena parte de la criptografía de uso actual.

Entre las primitivas criptográficas amenazadas por la informática cuántica, la criptografía de clave pública es sin duda la más afectada. La seguridad de los esquemas criptográficos de clave pública (incluidos RSA, RSA-PSS, ECDH y ECDSA) se basa en la presunta dificultad de ciertos problemas matemáticos, como pueden ser el problema RSA y del logaritmo discreto. Disponiendo sólo de ordenadores clásicos, estos problemas son difíciles de resolver. Sin embargo, en 1994, Shor desarrolló un algoritmo cuántico que los podría romper eficientemente. Entonces, si se llega a construir un ordenador cuántico suficientemente potente, todos los estándares criptográficos de clave pública actuales podrían volverse vulnerables, perjudicando así la seguridad de la amplia gama de aplicaciones de la criptografía de clave pública, incluidos el cifrado, las firmas digitales, las monedas digitales, los intercambios de claves o las marcas de tiempo. Por lo tanto, estas aplicaciones deberían adoptar primitivas criptográficas que sean seguras contra ataques cuánticos conocidos, conocidos como primitivas post-cuánticas.

A fin de promover una transición global hacia la criptografía post-cuántica, el Instituto Nacional de Estándares y Tecnología (del inglés, NIST) ha lanzado un proceso de estandarización de la criptografía post-cuántica. Este proceso es abierto y transparente, y tiene como objetivo seleccionar las próximas primitivas criptográficas post-cuánticas. Comenzó en 2016 con un total de 82 candidatos, y ahora está en la tercera ronda de evaluación, con sólo siete candidatos finalistas y ocho candidatos adicionales.

Una vez seleccionados los estándares de primitivas criptográficas post-cuánticas, su adopción conllevará una intensa etapa de implementación para llevarlos al uso general. Las implementaciones hardware requerirán procesadores optimizados, a fin de que ejecuten los esquemas seleccionados de manera eficiente y segura. Entre las plataformas existentes, las basadas en arquitecturas de código abierto y libres de derechos de autor pueden inspirar una mayor confianza debido a la transparencia de sus diseños, además de tener ventajas jurídicas y económicas en el desarrollo de aplicaciones personalizadas. Esto es lo que motiva el proyecto DRAC para seleccionar RISC-V como arquitectura para el desarrollo hardware de los candidatos del proceso del NIST.

"DRAC: Designing RISC-V-based Accelerators for Next Generation Computers" es un proyecto de investigación que se inició en junio de 2019, liderado por el Barcelona Supercomputing Center-Centro Nacional de Supercomputación (BSC-CNS) en cooperación con la Universidad Politécnica de Cataluña (UPC), la Universidad de Barcelona (UB), la Universidad Autónoma de Barcelona (UAB) y la Universidad Rovira i Virgili (URV). El proyecto se enmarca en el programa Estrategia de investigación e innovación para la especialización inteligente de Cataluña (RIS3CAT), y el 50% de la financiación proviene del Fondo Europeo de Desarrollo Regional (FEDER).

El proyecto DRAC tiene por objetivo fabricar un procesador y varios aceleradores basados en la tecnología RISC-V. Los chips desarrollados deberían ser energéticamente eficientes, de alto rendimiento y adecuados para la supercomputación y los cálculos a gran escala. Un objetivo secundario de DRAC es fomentar la soberanía tecnológica estratégica de Europa, ya que todo el continente depende actualmente de infraestructuras externas para el diseño y fabricación de chips, con la consecuente exposición a vulnerabilidades hardware.

RISC-V ofrece ciertas ventajas de seguridad respecto de otros ISA. En primer lugar, los diseños RISC-V son auditables gracias a la transparencia del ISA, dado que la visión completa de los diseños de los chips no está restringida al proveedor. Una segunda ventaja es que la naturaleza de código abierto de los diseños disponibles públicamente puede ayudar a prevenir vulnerabilidades de hardware, tales como las recientes Spectre y Meltdown. En tercer lugar, la flexibilidad asociada al uso de extensiones puede simplificar los diseños de los chips, produciendo hardware menos vulnerable y facilitando el proceso de depuración. Y, por último, cuenta con un conjunto de instrucciones sencillo y coherente, en contraste con otras ISA con problemas de instrucciones heredados, lo que podría reducir las vulnerabilidades del hardware.

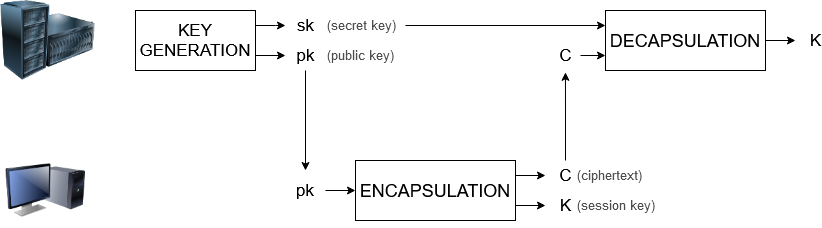

Motivado por la amenaza de la computación cuántica sobre la criptografía de clave pública actual, y también por las ventajas que ofrece RISC-V, el proyecto DRAC tiene como objetivo la aceleración de esquemas criptográficos post-cuánticos de clave pública. Se han seleccionado tres de los siete candidatos finales del proceso de estandarización del NIST, y se planea el diseño de aceleradores seguros y de extensiones RISC-V para estos esquemas. Las tareas de desarrollo se basan en las implementaciones facilitadas al NIST, a fin de evitar ataques de canal lateral y otros errores de implementación. Los resultados de la aceleración hardware se desplegarán en chips RISC-V en un período de 2 años.

Imagen: Protocolo de firma digital utilizando los tres algoritmos que constituyen un DS: Generación de claves, Firmar y Verificar.