El processador Sargantana comptarà amb suport hardware per entorns virtualitzats, complint l'especificació de RISC-V Privileged Architecture [1]. Això permet que entorns virtualitzats, com màquines virtuals, s'executin de manera més eficient.

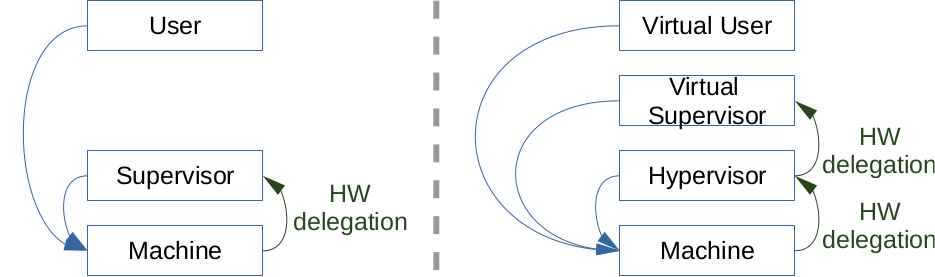

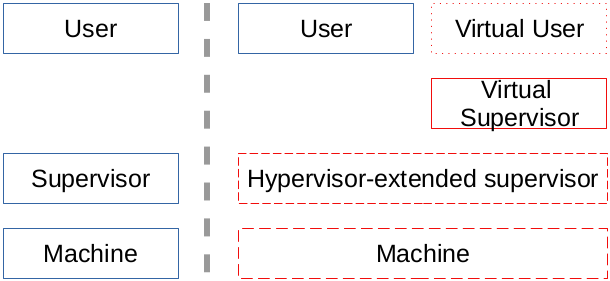

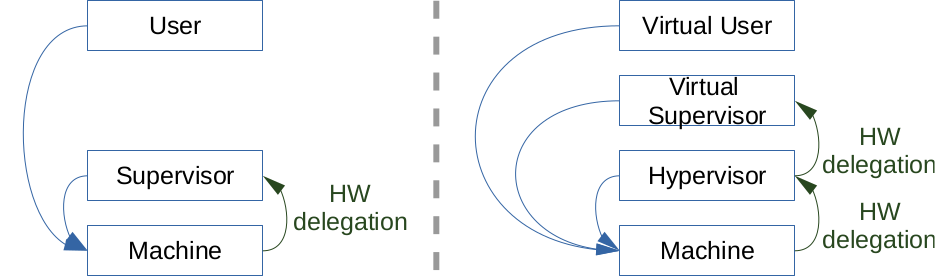

A efectes pràctics, vol dir que s'afegeix un nou mode d'execució (hipervisor) que virtualitza els modes d'execució habituals (usuari-virtual supervisor-virtual). Per afegir aquest suport al processador Sargantana, s'han de modificar certes

parts del nucli, en particular:

Conjunt de registres hardware El nucli ja disposa de registres de control i estat (CSRs) per rastrejar i controlar els modes d'execució habituals (usuari, supervisor i màquina). La nova extensió requereix modificar alguns d'aquests registres per activar la virtualització, així com afegir nous CSRs pel nou mode (hipervisor) i pels nous modes virtualitzats (usuari-virtual i supervisor-virtual).

Gestió de les interrupcions i excepcions Per defecte, totes les interrupcions i excepcions són tractades pel mode màquina, que pot realitzar el tractament o invocar a una rutina del nivell superior. Donat que aquest tractament pot ser lent, es disposa d'un mecanisme hardware que permet delegar el tractament en un nivell superior (evitant els salts intermedis). Amb el nou mode hipervisor, cal afegir un nou nivell de delegació i afegir tot un conjunt d'excepcions noves pròpies dels entorns virtualitzats.

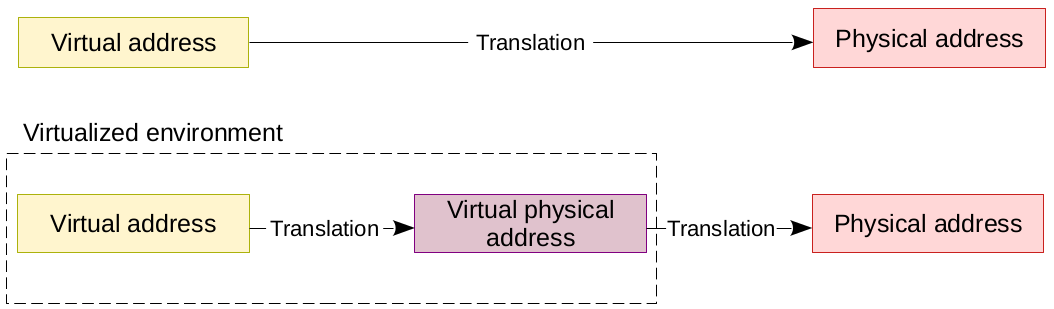

Gestió de l'espai d'adreces Cal afegir suport per entorns virtualitzats al mòdul que s'encarrega de protegir i traduir les adreces virtuals a adreces físiques. En aquests entorns totes les adreces físiques estan virtualitzades i, per tant, s'han de fer dos traduccions: 1) per traduir una adreça virtual a una adreça física dins l'entorn virtualitzat (física virtual) i 2) per traduir aquesta física virtual i obtenir l'adreça física real dintre la màquina. Cal tenir present que aquesta segona fase de traducció no només afecta a l'adreça física virtual resultat de la primera fase, sinó a totes les estructures intermèdies (taules de pàgines) usades en la pròpia traducció.

Noves instruccions L'especificació del hypervisor també inclou noves instruccions per gestionar la memòria dels entorns virtualitzats.

A part de les modificacions del processador, també s'han de fer nous programes

de prova que tinguin en compte la verificació d'aquests entorns virtualitzats i que les modificacions implementades no afectin el funcionament normal del processador en entorns no virtualitzats.

Referencies

[1] RISC-V Fundation. RISC-V Privileged Architecture, version 20210915-Public-Review-draftn, https://github.com/riscv/riscv-isa-manual/releases/tag/riscv-privileged-20210915-public-review