Un dels objectius fonamentals que persegueix el disseny de processadors és aconseguir un alt nivell de rendiment. Al llarg dels anys han sorgit diverses propostes, tant a l'acadèmia com a la indústria, que han explorat idees noves per aconseguir aquest objectiu, aprofitant l'evolució tecnològica dictada per la Llei de Moore. Tot i això, el disseny de processadors no ha deixat de ser una tasca desafiant en què es busca mantenir un balanç entre complexitat i rendiment.

En aquest sentit, els processadors superescalars, els quals són màquines de processament capaces d'executar múltiples instruccions per cicle de rellotge, han demostrat ser eficaços en aprofitar el paral·lelisme a nivell d'instrucció implementant tècniques de planificació dinàmica, que conjugades amb una unitat de gestió de memòria eficient, i acceleradors especialitzats, resulten en un alt aprofitament dels recursos del maquinari, aconseguint un elevat percentatge d'instruccions executades per cicle de rellotge.

El projecte DRAC té com a objectiu el disseny, la verificació i la fabricació d'un processador d'alt rendiment integrant diversos acceleradors, a més d'altres prestacions, en un mateix system-on-chip (SoC). Amb la finalitat d'assolir aquest objectiu, en un esforç conjunt entre el BSC i el CIC-IPN, s'ha proposat el disseny i la implementació del processador Lagarto Ka, un processador súper-escalar de 2-vies i 64-bits implementat en una microarquitectura de 12 etapes amb execució fora d'ordre basat en el conjunt d'instruccions de RISC-V.

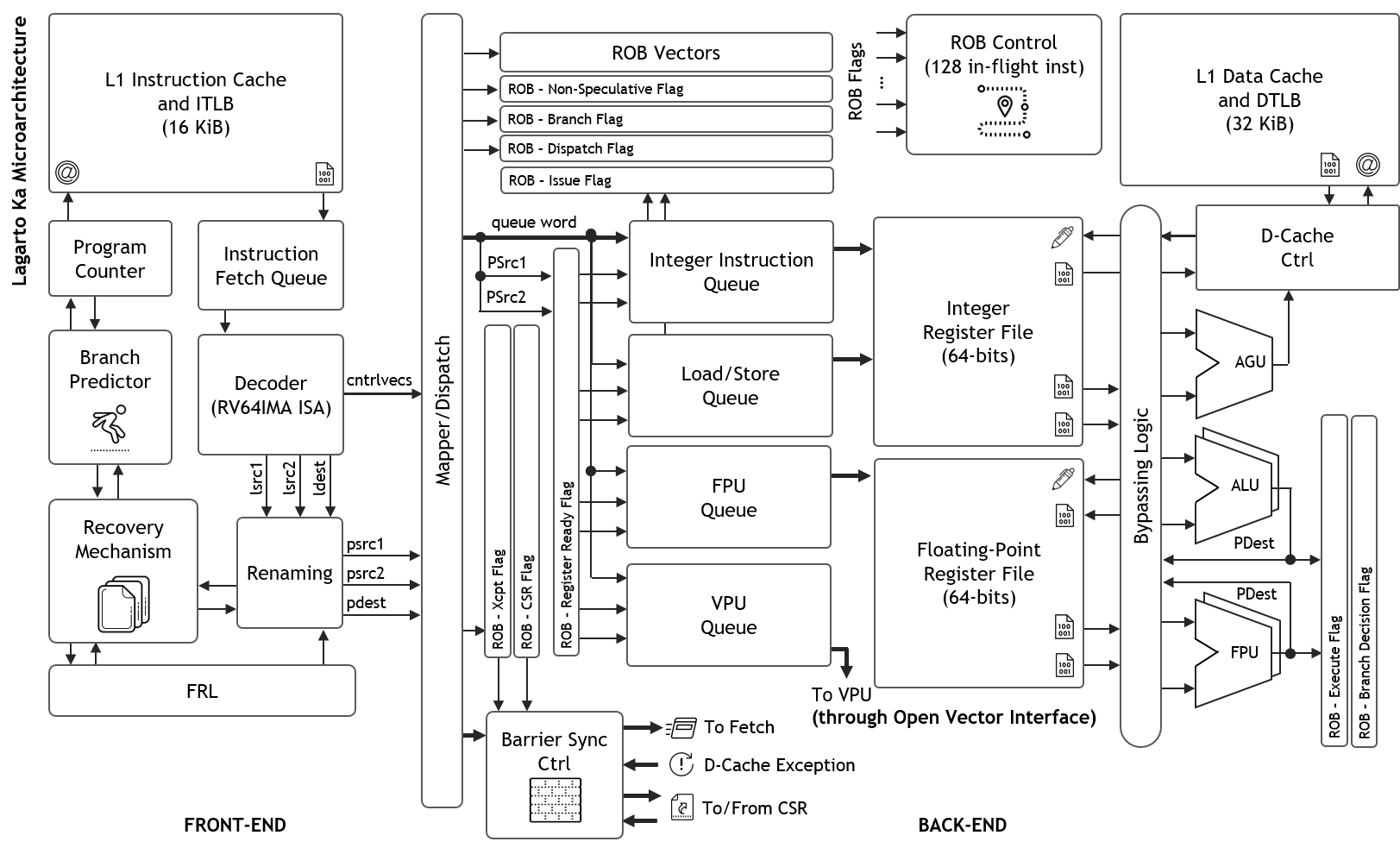

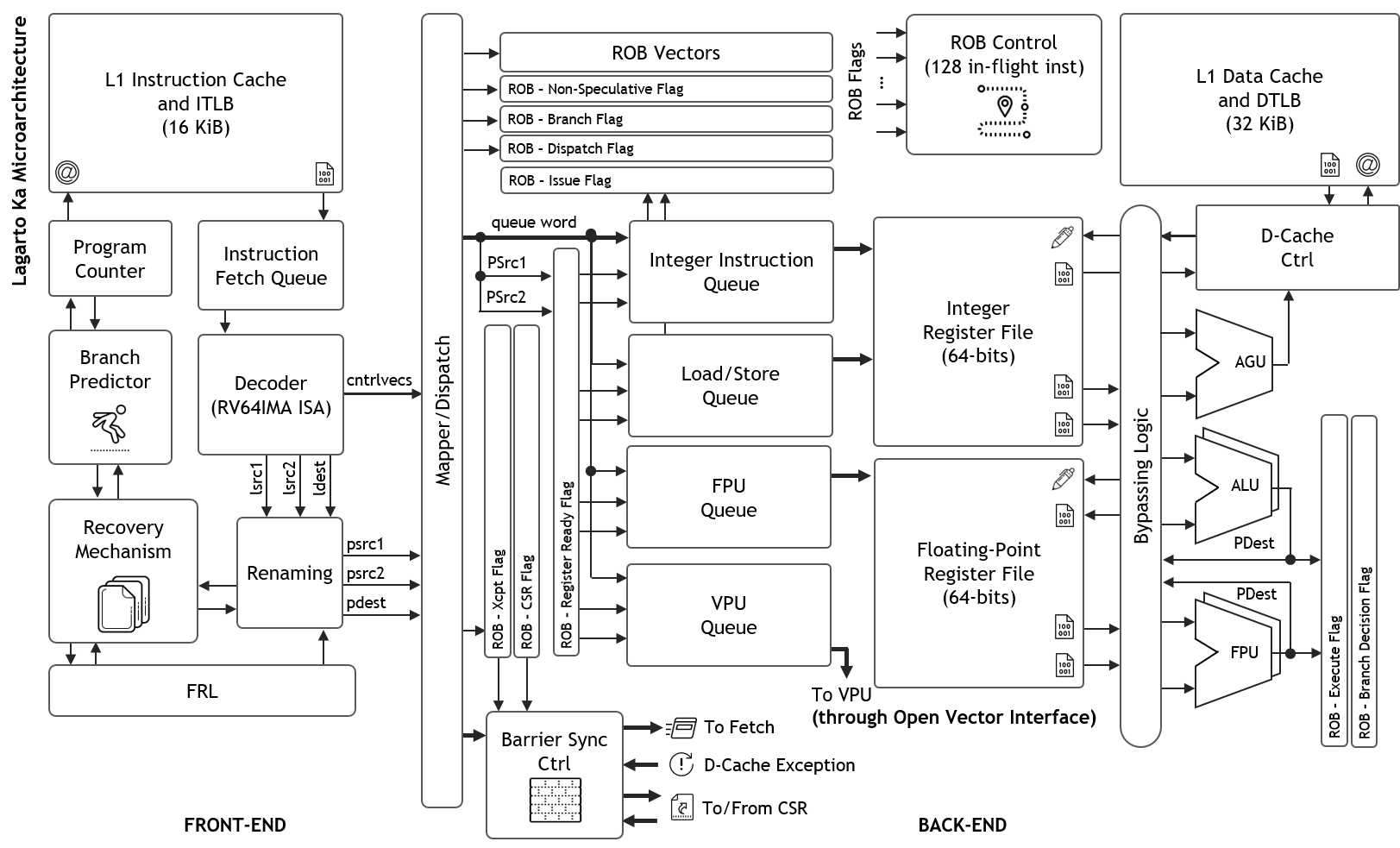

Com s'observa a la Figura 1, la microarquitectura del processador Lagarto Ka es divideix en dos blocs fonamentals de processament: el Front-End i el Back-End.

El Front-End és la part del processador a càrrec de mantenir un flux constant d'instruccions al pipeline que han de ser portades des de la memòria cau d'instruccions, descodificades, i renombrades, per després ser distribuïdes en el camí de dades que correspongui a cada instrucció per ser executada correctament. El renombrat de registres és fonamental en aquesta etapa del processament ja que amb aquest s'aconsegueixen resoldre les falses dependències entre instruccions, mantenint només les dependències reals, cosa que permet optimitzar l'execució d'instruccions independents trencant l'ordre del programa.

Addicionalment, el Front-End integra un predictor de salts que permet accelerar la cerca d'instruccions en detectar salts al codi del programa sense la necessitat d'haver estat descodificats. Finalment, és possible restaurar el context del processador a un estat previ davant de qualsevol error gràcies al fet que es compta amb un mecanisme de recuperació que permet executar de manera efectiva els fluxos d'instruccions especulatius.

El segon bloc de processament, el Back-End, ha estat dissenyat per explotar el paral·lelisme a nivell d'instrucció que ofereix el renombrat dels registres, avançant l'execució d'instruccions tan aviat com els seus operands font estiguin llestos, sense importar l'ordre inicial al que entren al pipeline. Aquest procés se'l coneix com a execució fora d'ordre.

L'execució fora d'ordre dins del processador Lagarto Ka és controlada gràcies a dues estructures principals: les cues d'emissió fora d'ordre encarregades d'enviar tantes instruccions com sigui possible a les unitats d'execució cada cicle de rellotge, i el buffer de reordenament (ROB), que monitoritza l'ordre del conjunt d'instruccions que es troben actives al Back-End, determina quan s'han d'alliberar els recursos de hardware una vegada que les instruccions abandonen el pipeline.

Atès que el consum d'energia és crític en l'ús de sistemes encastats, el processador Lagarto Ka integra tècniques de baix consum d'energia que busquen mitigar aquest problema.

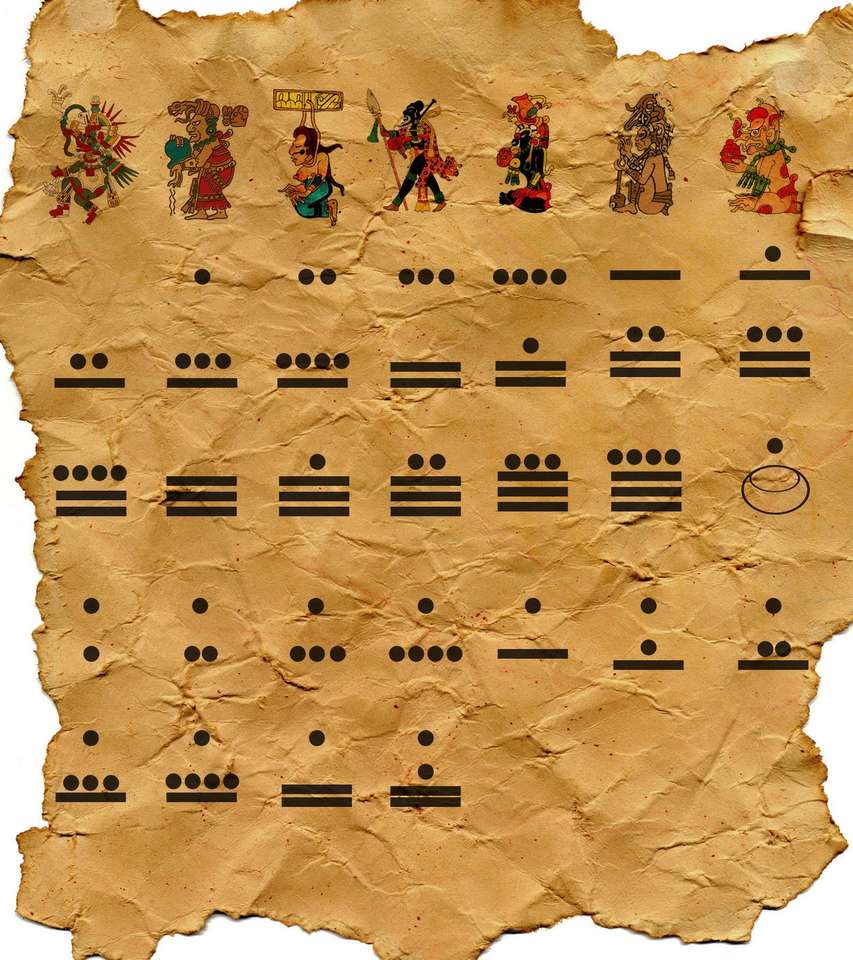

Lagarto Ka és la primera proposta d’alt rendiment de la família de processadors Lagarto. El seu nom està inspirat en la numeració maia amb què també s'ha identificat els primers dissenys fabricats a DRAC. És així que la primera versió, un processador escalar en ordre que emet una instrucció per cicle de rellotge, ha estat anomenada Lagarto Hun, mentre que Lagarto Ka ha estat dissenyat per emetre dues instruccions per cicle.

Lagarto Ka és el nucli del xip on s'integren els diferents acceleradors desenvolupats a DRAC, un projecte que vol obrir pas a noves propostes de disseny des de l'acadèmia dins del camp de l'Arquitectura de Computadors, inicialment detonades per iniciatives de codi obert com la de RISC-V, cercant que en un futur no gaire llunyà sigui possible aprofitar aquestes propostes en productes d'ús especialitzat o domèstic.