David Castells-Rufas, Santiago Marco-Sola, Juan Carlos Moure, Quim Aguado, Antonio Espinosa

Els filtres de pre-alineament proposen mètodes útils per reduir els requeriments computacionals de les aplicacions de mapeig de seqüències genòmiques.

La majoria dels filtres estan basats en estimacions o càlculs de la distància d'edició entre les seqüències curtes d'entrada i les localitzacions candidates al genoma de referència. Típicament es fa servir un subconjunt dels elements de la taula generada mitjançant programació dinàmica al computar la distància de Levenshtein entre les seqüències curtes i la referència.

Algunes implementacions FPGA d'aquests filtres pre-alineament utilitzen eines clàssiques HDL (Hardware Description Language) que limiten la seva portabilitat. Actualment, les eines HLS (High Level Synthesis) per a C/C++ poden ser utilitzades a la majoria d'acceleradores computacionals FPGA disponibles als principals proveïdors de computació al núvol. El nostre treball ha consistit en re-implementar i optimitzar diversos filtres publicats a l'estat de l'art utilitzant eines HLS basades en C/C++ per expandir la seva portabilitat a un ampli ventall de sistemes amb capacitats d'executar el runtime OpenCL.

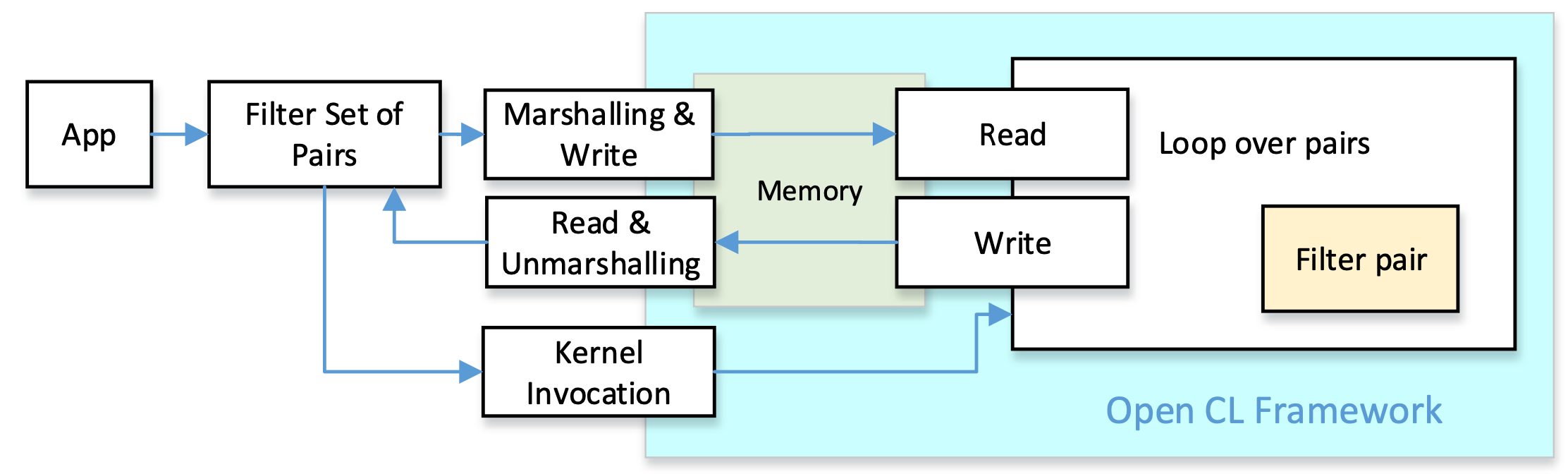

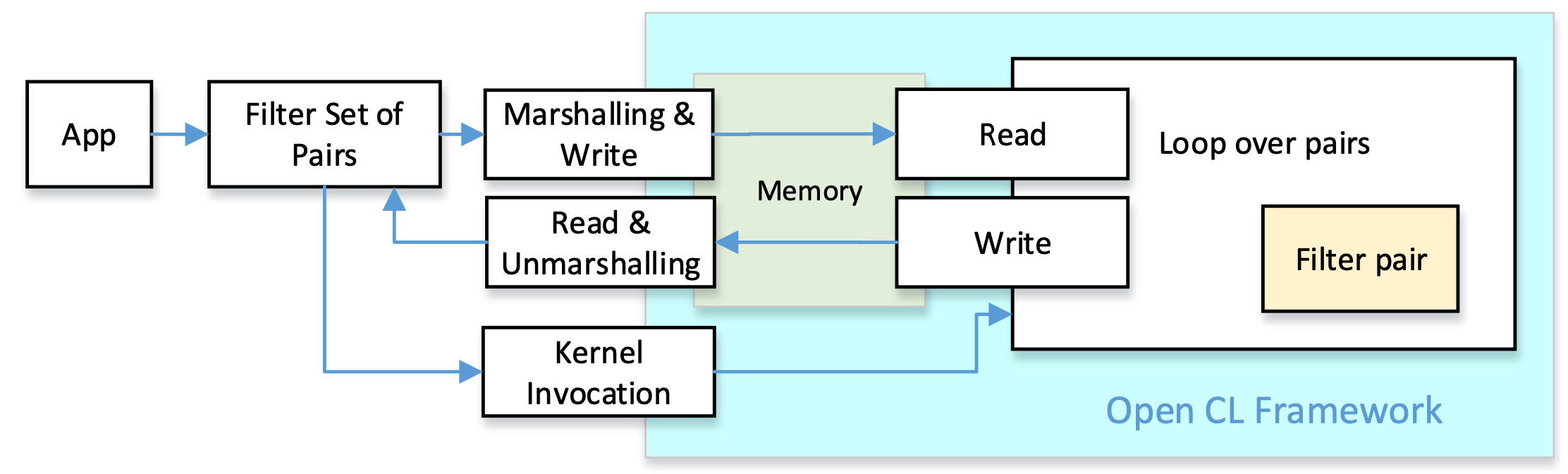

El nostre objectiu és crear filtres pre-alineament que puguin ser integrats a centres de dades equipats amb acceleradores FPGA de forma simple. Hem seleccionat OpenCL com l'entorn d'implementació FPGA amb major disponibilitat a les plataformes existents. Tots els filtres estudiants comparteixen el mateix objectiu: comparar un patró amb un text per obtenir una estimació de la distància entre tots dos. Aquest procés s'implementa en C/C++ amb funcions que mantenen el mateix número de paràmetres i retornen el mateix número de valors. Podem utilitzar aquesta encapsulació per a implementar un conjunt comú de funcions per a tots els filtres tant al servidor com a l'accelerador com es mostra a l'esquema lògic:

L'anàlisi algorítmic que permet traduir les propostes existents d'HDL a HLS basat en C/C++ te com objectiu simplificar els mètodes i generar oportunitats per a l'optimització. La combinació d'aquests dos aspectes ha permès simplificar els algoritmes i millorar el rendiment reduint l'ús de recursos.