En el projecte DRAC estem dissenyant SoCs (de l’anglès System-on-Chip) que inclouen processadors basats en l’arquitectura RISC-V, diferents acceleradors i un conjunt de blocs analògics com son un PLL, un SerDes, un ADC i SPADs (de l’anglès, Phase-Locked Loop, Serializer Deserializer, Analog to Digital Converter i Single Photon Avalanche Diode, respectivament). D’aquests blocs analògics, el PLL i el SerDes permeten augmentar el nombre d’instruccions executades pel processador; el PLL permet augmentar la freqüència de treball mentre que el SerDes habilita comunicacions més ràpides amb les memòries externes. D’altra banda, l’ADC permet interactuar amb sensors analògics i els SPADs son una eina per poder habilitar la criptografia quàntica.

A l’hora de planificar l’estratègia d’integració dels diferents elements del SoC, s’ha de considerar que treballarem amb un disseny de senyal mixta. Tot i així, com els circuits que ocupen més àrea i els més complexes son els digitals, l’estratègia escollida és la DoT (de l’anglès, Digital On Top). Això vol dir que començarem a treballar com si el SoC fos purament digital, i a mig camí hi afegirem la informació dels blocs analògics que s’han dissenyat per separat.

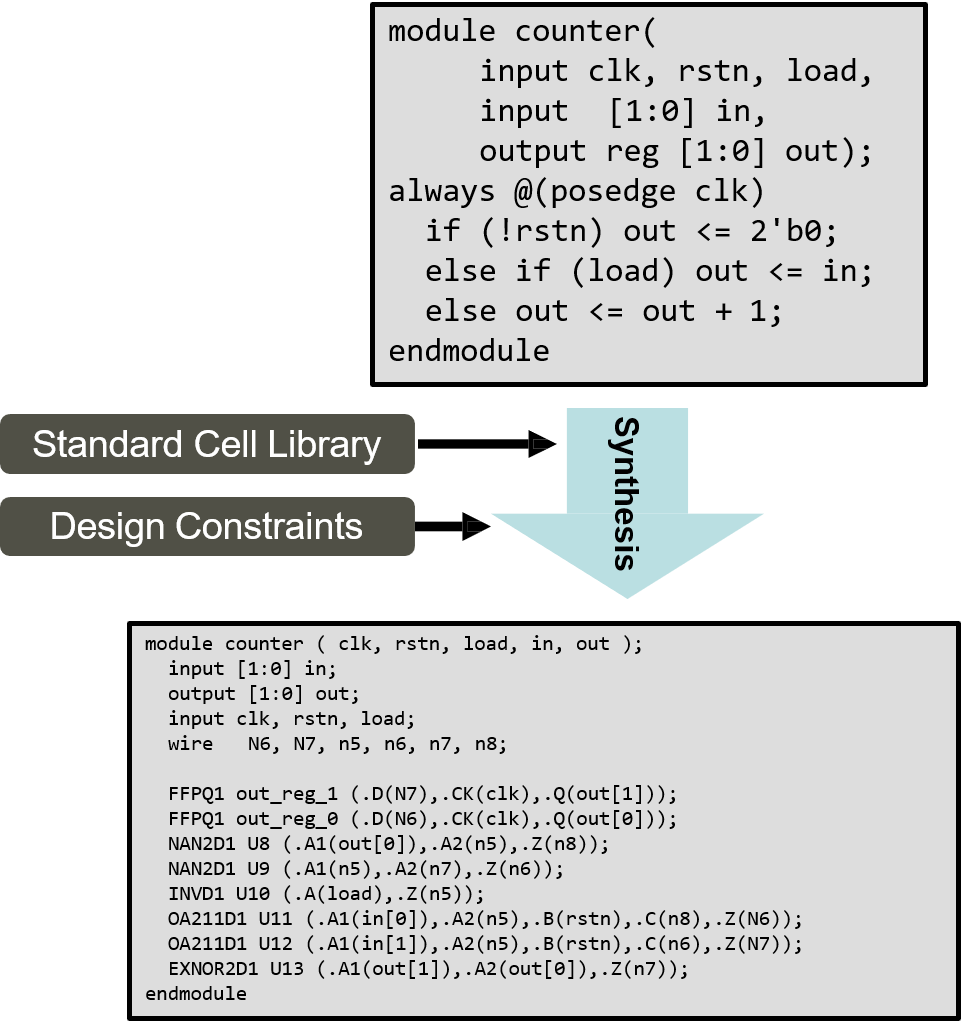

Cada bloc analògic es dissenya seguint el flux analògic, emprant l’eina “virtuoso” de Cadence®. En canvi, els dissenys digitals com el processador o els acceleradors es codifiquen amb llenguatge RTL (de l’anglès , Register-Transfer Level), que ens permet descriure el comportament del circuit que volem dissenyar i verificar-lo amb simulacions. Un cop estem segurs que el circuit dissenyat té el comportament esperat, es necessita traduir el comportament descrit a un conjunt de portes lògiques que facin la mateixa funció. Aquest pas s’anomena síntesis lògica, i per a realitzar-la son necessàries la descripció del nostre circuit, la informació de portes disponibles de la tecnologia que fem servir i incloure les limitacions del circuit (figura 1).

Fig.1: Exemple esquemàtic del procés en una síntesis lògica

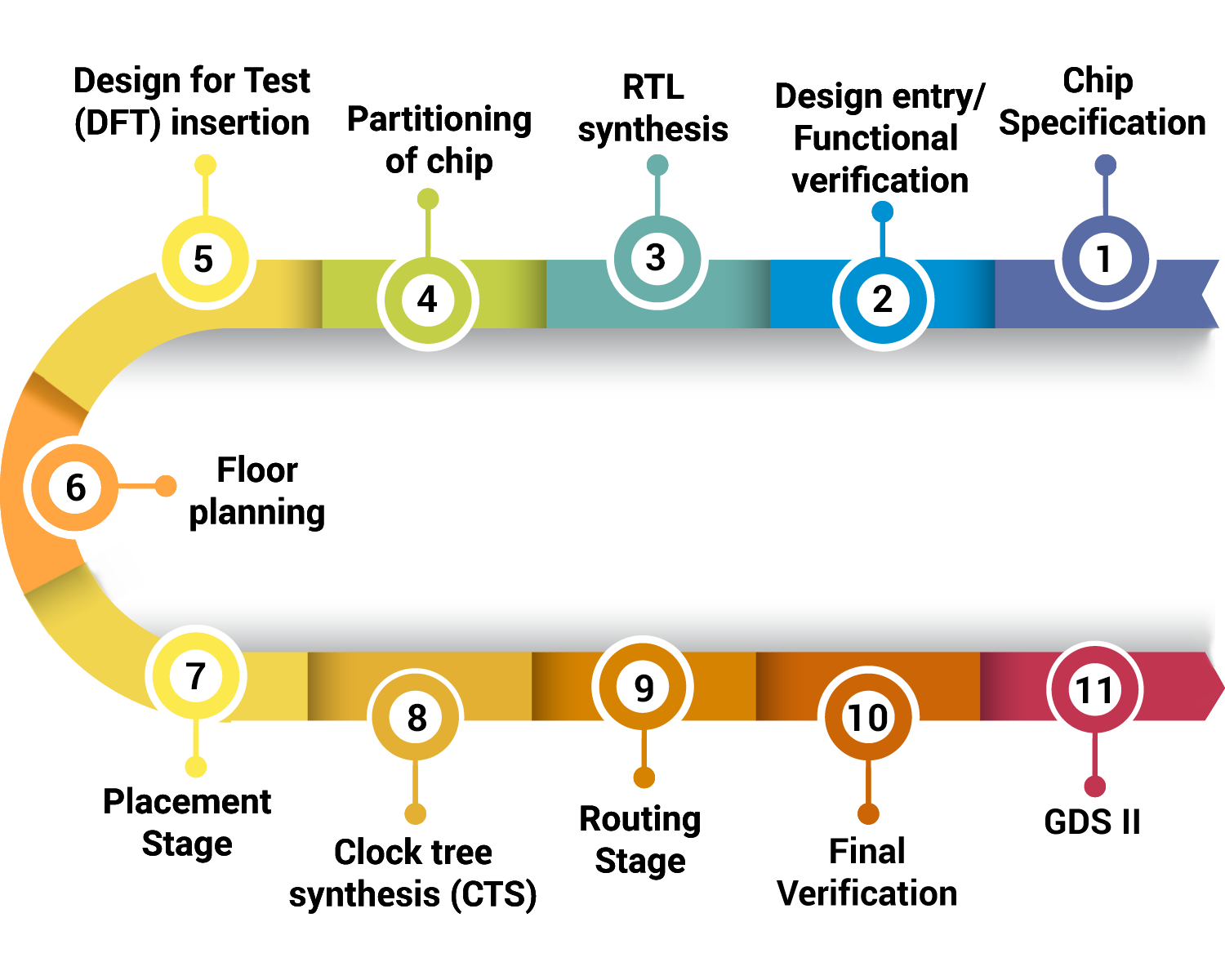

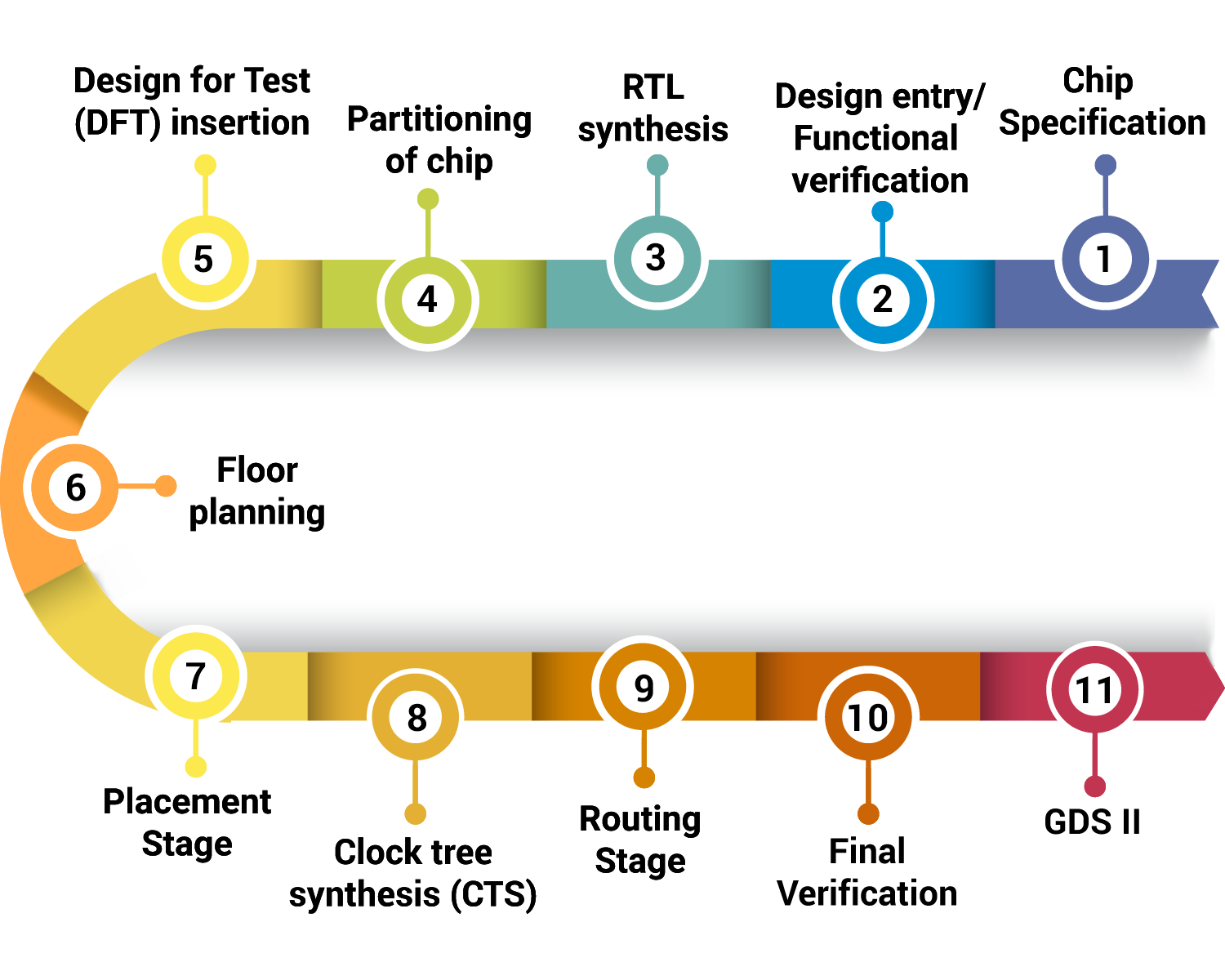

Un cop finalitzada la síntesis obtenim un fitxer, anomenat “netlist”, on hi trobarem el circuit digital que hem dissenyat expressat en portes lògiques disponibles en la tecnologia escollida. El següent pas consisteix en distribuir les cel·les lògiques, blocs analògics, GPIOs i memòries en una àrea determinada i, a més, realitzar les connexions entre ells. Aquest pas s’anomena síntesis física, i es pot resumir, molt breument, en 5 etapes: Floorplan, Placement, Clock tree synthesis (CTS), Routing i Signoff o Final Verification (veure figura 2, del pas 6 al 10).

En l’etapa Floorplan fem la distribució del nostre SoC, l’àrea que ocuparan els circuits digitals, on posarem les memòries i GPIOs, on posarem els blocs analògics i com alimentarem els circuits. En l’etapa Placement, es realitza una primera disposició de les portes lògiques per a comprovar que el disseny realment es pot realitzar, considerant l’espai disponible i les limitacions temporals que volem aconseguir. En l’etapa CTS, es realitza la distribució de la xarxa dels rellotges del sistema. En l’etapa Routing, es realitza la connexió física, a través de línies de metall, de les portes lògiques. Finalment, l’etapa Signoff serveix per tancar el xip; aquí s’executen comprovacions temporals i tecnològiques per saber si el xip compleix les limitacions temporals que desitgem i, també, si el xip pot ser fabricat. Aquesta última etapa finalitza generant un arxiu GDS II que, en resum, és el que necessita la fabrica de semiconductors per a fabricar el xip.

Fig.2: Flux esquemàtic dels passos necessaris per a dissenyar un xip, des de la idea inicial al fitxer que s’envia a la fabrica de semiconductors. Ressaltar que, els passos continguts entre l’etapa 6 i l’etapa 10 és el que anomenem síntesis física. Imatge extreta de: https://www.einfochips.com/blog/asic-design-flow-in-vlsi-engineering-services-a-quick-guide/