El pasado mes de febrero de 2022 se envió a Globalfoundries (a través de Europractice) el diseño del procesador Sargantana para su fabricación. Una vez diseñado y fabricado el chip, el siguiente paso será su validación, que nos permitirá determinar si las características finales se corresponden con las especificaciones iniciales. Para este efecto, se ha diseñado un sistema de test basado en PCB (Printed Circuit Board) que permitirá la monitorización de este dispositivo. Esta monitorización se realizará testeando directamente los diferentes bloques del chip e interconectando el sistema de test con un sistema de caracterización externo basado en FPGA a través de un bus de alta velocidad SERDES.

En este escrito explicamos las características del sistema de test basado en PCB: el estudio y simulación de las pistas de interconexión, para poder asegurar la integridad de la señal. La estructura y el número de capas, que permiten reducir las emisiones electromagnéticas (EMIs) y la reducción del ruido en modo común y en modo diferencial.

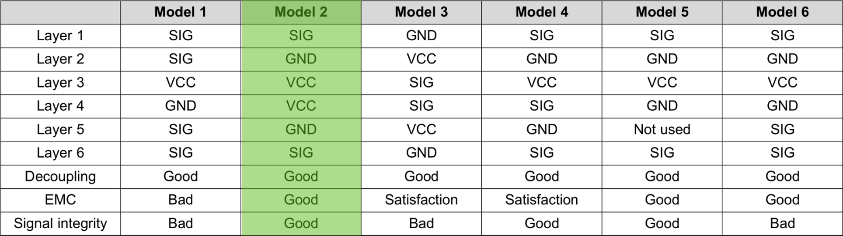

El sistema de test se diseñó utilizando la herramienta de diseño Xpedition PCB © EDA, que nos permitía además la simulación de las pistas de transmisión a partir de los ficheros de diseño del PCB. También nos sugería opciones que permitían maximizar la integridad de la señal y disminuir el ruido en las líneas que conectaban el microprocesador con los diferentes chips de memoria integrados en la PCB. Además de estas líneas, se simularon las pistas de SERDES, ya que estas eran líneas diferenciales que trabajaban a velocidades muy elevadas. Finalmente comentar que, aunque inicialmente se pensó en trabajar con un PCB de cuatro capas, se optó por ampliarlas a 6 para minimizar el ruido y maximizar la integridad de la señal. Observando las líneas que interconectan el microprocesador con los chips de memoria y SERDES, se puede comprobar una ondulación de las pistas. Este tipo de diseño es habitual en sistemas de circuitos de alta velocidad, ya que permite que la información transmitida por todas las líneas en paralelo llegue al mismo tiempo a su destino.

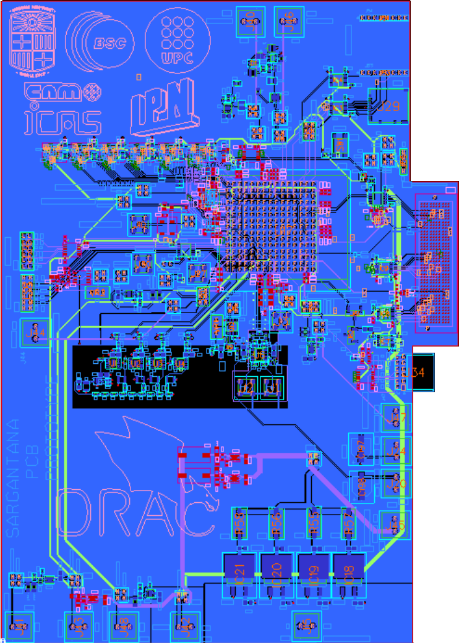

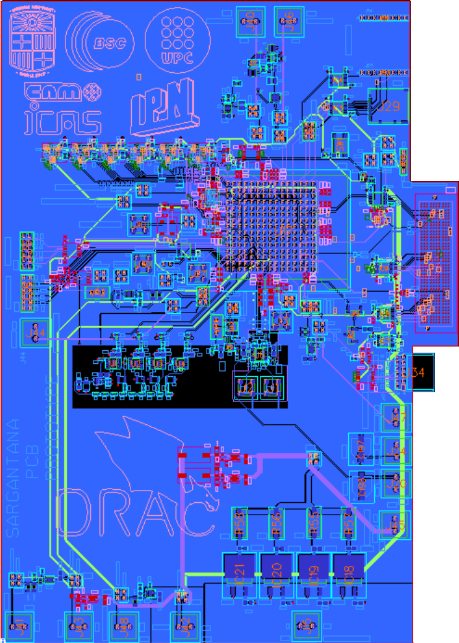

La figura 1 muestra la cara superior del diseño PCB enviado ya a fabricar a nuestro distribuidor: la empresa Rompal Ingenieros S.A. La figura 2 muestra la estructura de capas escogida, siguiendo las reglas de diseño del documento de Texas Intruments: High-Speed Layout Guidelines (SCAA082A).

El sistema de test permite alimentar todos los componentes de la placa internamente, a partir de una entrada de 5V que genera las señales de alimentación de 3.3V para los diferentes interfaces de conexión, como son las interficies serie UART y SPI o la interficie de programación serie JTAG;, 2.5V utilizados para alimentar el conector FMC de la placa de la FPGA; 1.8V para las memorias HyperRam y las entrada/salidas del procesador y 0.8V para el núcleo del procesador. El diseño de la placa de test nos permite también alimentar específicamente cada uno de los bloques de alimentación a través de conectores y utilizando fuentes externas.

El sistema de relojes que incorpora el PCB generan las señales de referencia para el procesador y para el ADC. El oscilador de referencia del procesador trabaja a una frecuencia de 100 MHz, mientras que el oscilador del ADC trabaja a 26.5 MHz.

Resumiendo, en este escrito explicamos las características generales asociadas al diseño del sistema de test desarrollado para caracterizar el chip Sargantana. Se han comentado las simulaciones realizadas para obtener una correcta integridad de señal, las características del trazado de pistas, y algunos de los bloques más importantes que la conforman.