El passat mes de febrer de 2022 es va enviar a Globalfoundries, i a través d’Europractice, el disseny del processador Sargantana per a la seva fabricació. Un cop dissenyat i fabricat el xip, el següent pas serà la validació, que ens permetrà determinar si les característiques finals es corresponen amb les especificacions inicials. Per tal efecte, s’ha dissenyat un sistema de test basat en PCB (Printed Circuit Board) que permetrà la monitorització de l’esmentat dispositiu. Aquesta monitorització es realitzarà testejant directament els diferents blocs del xip i interconnectant el sistema de test amb un sistema de caracterització extern basat en FPGA a través d’un bus d’alta velocitat SERDES.

En aquest escrit expliquem les característiques del sistema de test basat en PCB: l’estudi i simulació de les pistes d’interconnexió, que ens permetrà assegurar la integritat del senyal. L’estructura i el nombre de capes, que permeten reduir les emissions electromagnètiques (EMIs) i la reducció de soroll en mode comú i en mode diferencial.

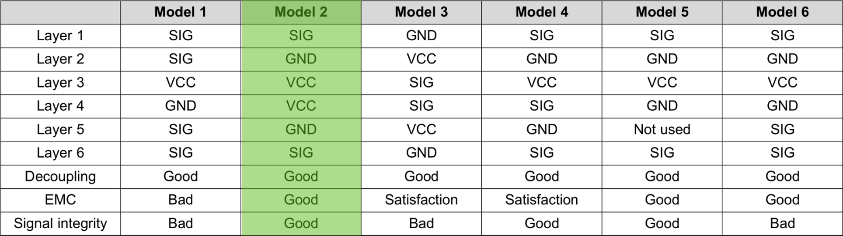

El sistema de test es va dissenyar utilitzant l’eina de disseny Xpedition PCB © EDA, que ens va permetre a més del disseny del PCB, la simulació de les pistes de transmissió a partir dels fitxers del propi disseny. També ens suggeria opcions que permetien maximitzar la integritat del senyal i disminuir el soroll en les línies que connectaven el microprocessador amb els diferents xips de memòria integrats en la PCB. També es van simular el traçat i la caracterització de les pistes de SERDES, ja que aquestes eren línies diferencials que treballen a velocitats molt elevades. Finalment comentar que, tot i que inicialment es va pensar en treballar amb un PCB de quatre capes, es va optar per ampliar-les a 6 per minimitzar el soroll i maximitzar la integritat del senyal. Observant les línies que interconnecten el microprocessador amb els xips de memòria i SERDES, es pot comprovar una ondulació de les pistes. Aquest tipus de disseny és habitual en sistemes de circuits d’alta velocitat, ja que permet que la informació transmesa per totes les línies en paral·lel arribin al mateix temps al seu destí.

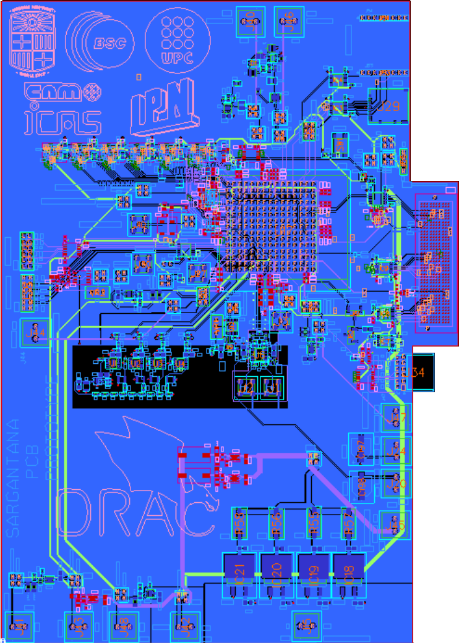

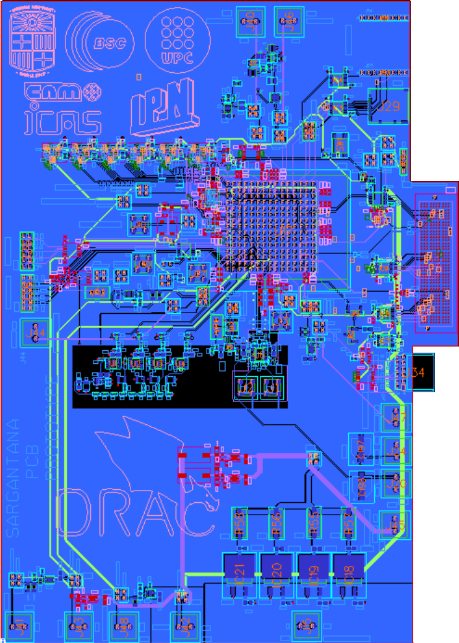

La figura 1 mostra la cara superior del disseny PCB enviat ja a fabricar al nostre distribuïdor: l’empresa Rompal Ingenieros S.A. La figura 2 mostra l’estructura de capes escollida, seguint les regles de disseny del document de Texas Instruments: High-Speed Layout Guidelines (SCAA082A).

El sistema de test permet alimentar tots els components de la placa internament, a partir de l’entrada de 5V, que generarà els senyals d’alimentació de 3.3V per a les diferents interfícies de connexió, com son les interfícies sèrie UART i SPI o la interfície de programació sèrie JTAG; 2.5V utilitzats per alimentar el connector FMC de la placa de la FPGA; 1.8V per a les diferents memòries HyperRAM i les entrades/sortides del processador; finalment, 0.8V per alimentar el nucli del processador. El disseny de la placa de test també ens permet alimentar específicament cada un dels blocs anteriorment esmentats a través de connectors i fonts d’alimentació externes.

El sistema de rellotges que incorpora el PCB generarà els senyals de referència necessaris pel processador i en concret per l’ADC que incorpora. L’oscil·lador de referència del processador treballa a una freqüència de 100 MHz, mentre que l’oscil·lador del ADC treballa a 26.5 MHz.

Resumint, en aquest escrit expliquem les característiques generals associades al disseny del sistema de test desenvolupat pel xip Sargantana. S’han comentat les simulacions i el treball realitzat per tal d’obtenir una correcta integritat del senyal, les característiques del traçat de pistes i alguns del blocs més importants que la conformen.