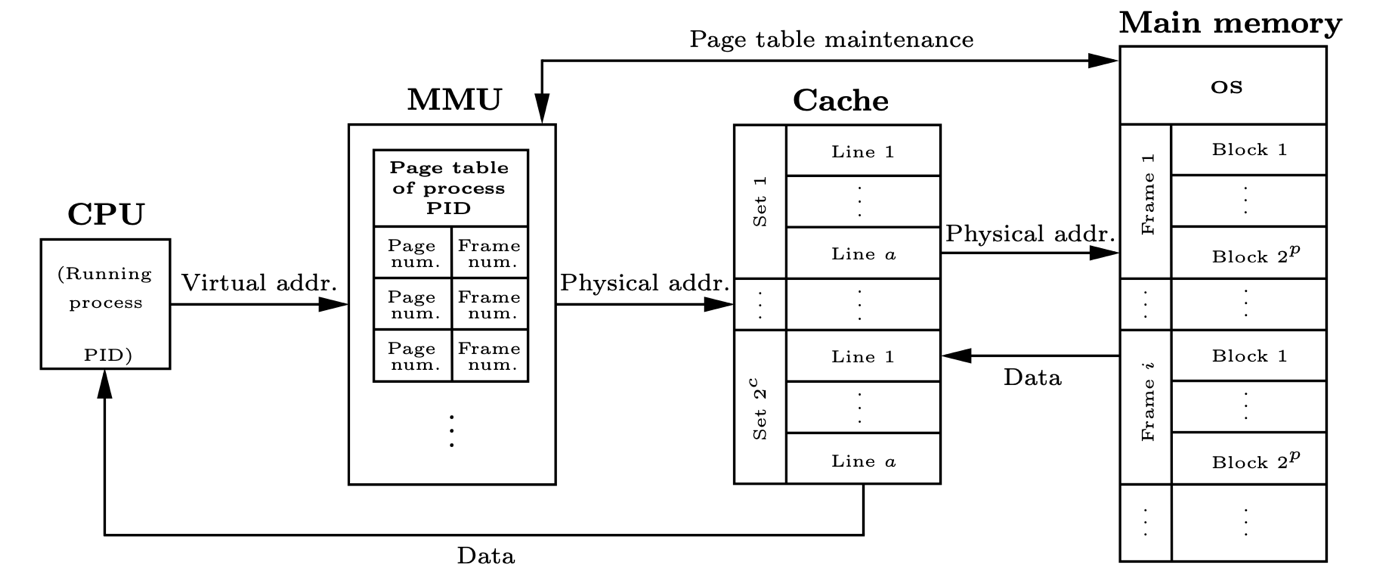

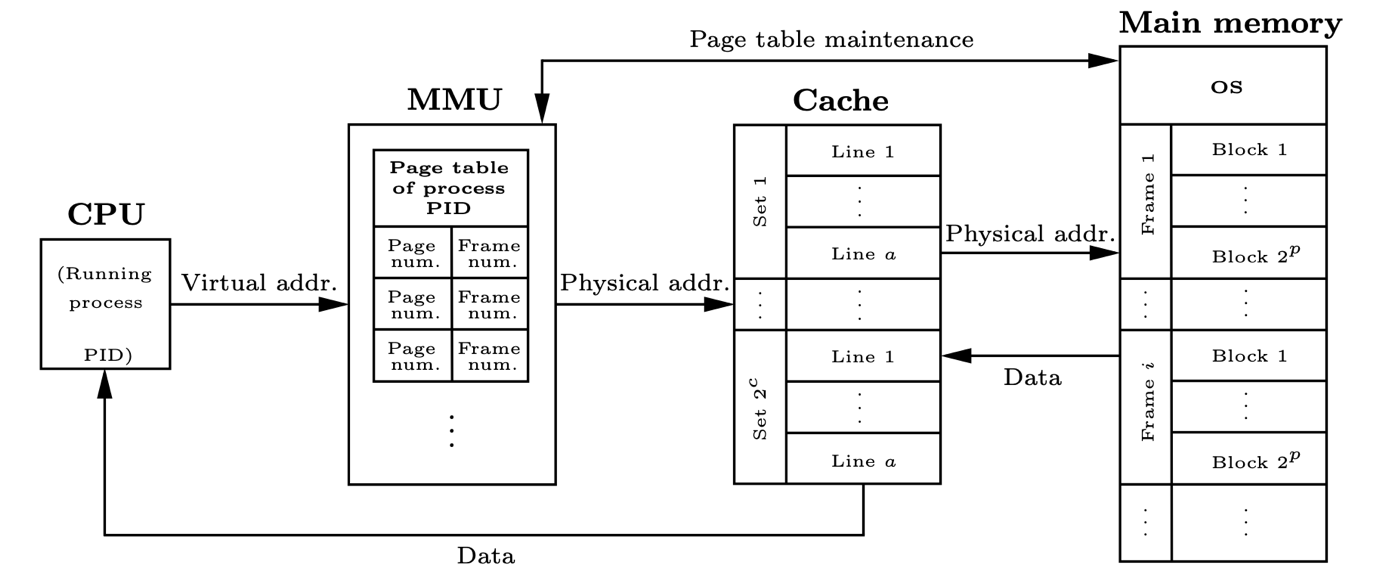

En la arquitectura informática, los cachés son componentes de almacenamiento de hardware diseñados para mitigar los problemas de alta latencia de los accesos a la memoria principal. La baja latencia inherente de los accesos a la memoria caché es vital para el rendimiento y, sin embargo, puede causar problemas de seguridad. La latencia de acceso aporta a los núcleos información de si los datos ya residían o no en la jerarquía de caché antes de que se produjera el acceso. Los ataques de canal lateral de caché permiten a los adversarios obtener información confidencial sobre los procesos en ejecución utilizando solo medidas de latencia de acceso y contención de la caché. Se ha demostrado que esta vulnerabilidad conduce a varios ataques de microarquitectura. Una solución que tiene como objetivo la protección contra los ataques basados en el acceso es la aleatorización de caché. Las memorias caché protegidas basadas en la aleatorización (RPC) mezclan las direcciones de la memoria caché para que los accesos se distribuyan aleatoriamente en la memoria caché. Sin embargo, se espera que cualquier RPC se vuelva inseguro si los atacantes tienen suficientes accesos.

Uno de los objetivos del proyecto DRAC era aportar soluciones hardware a este problema. Primero, analizamos las propiedades de seguridad de los RPC y aportamos una nueva noción de seguridad que captura la seguridad contra ataques conocidos como Prime+Probe y Evict+Probe. Luego, utilizando esta definición, obtenemos resultados que nos permiten garantizar la seguridad al elegir adecuadamente el período de cambio de claves, el algoritmo de generación de claves y el aleatorizador de caché, proporcionando así pruebas de seguridad para RPC bajo ciertos supuestos.

Este trabajo se presentará en la Conference on Cryptographic Hardware and Embedded Systems (CHES) 2022. La versión completa del documento está disponible en https://eprint.iacr.org/2022/440.pdf