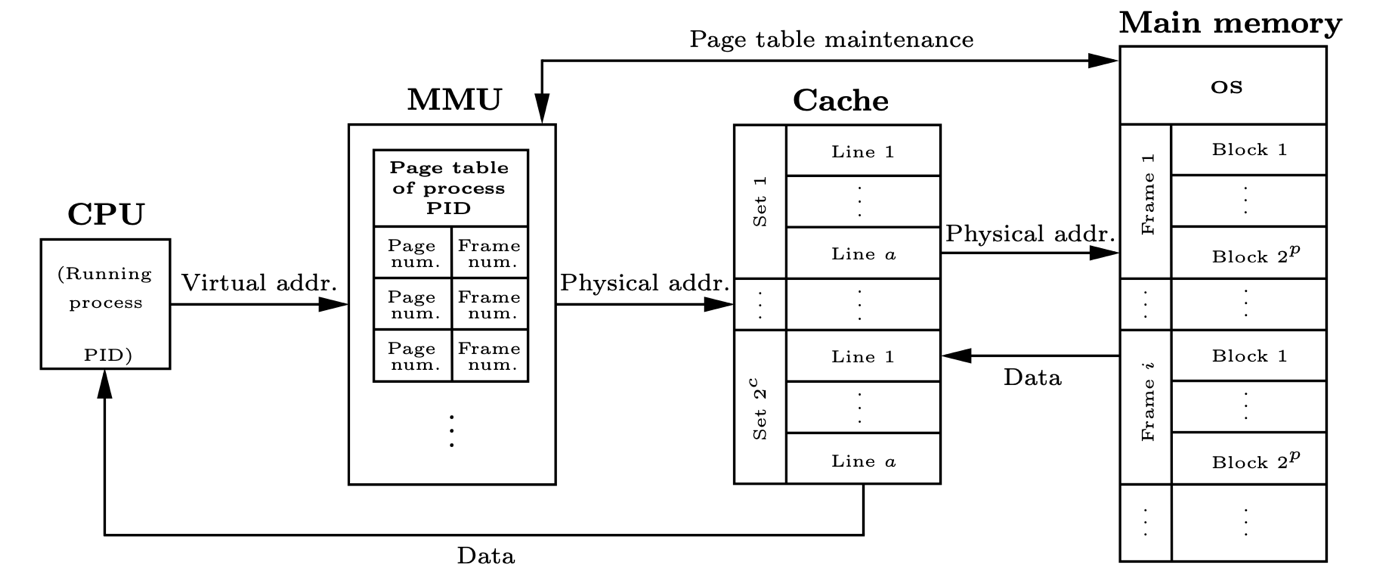

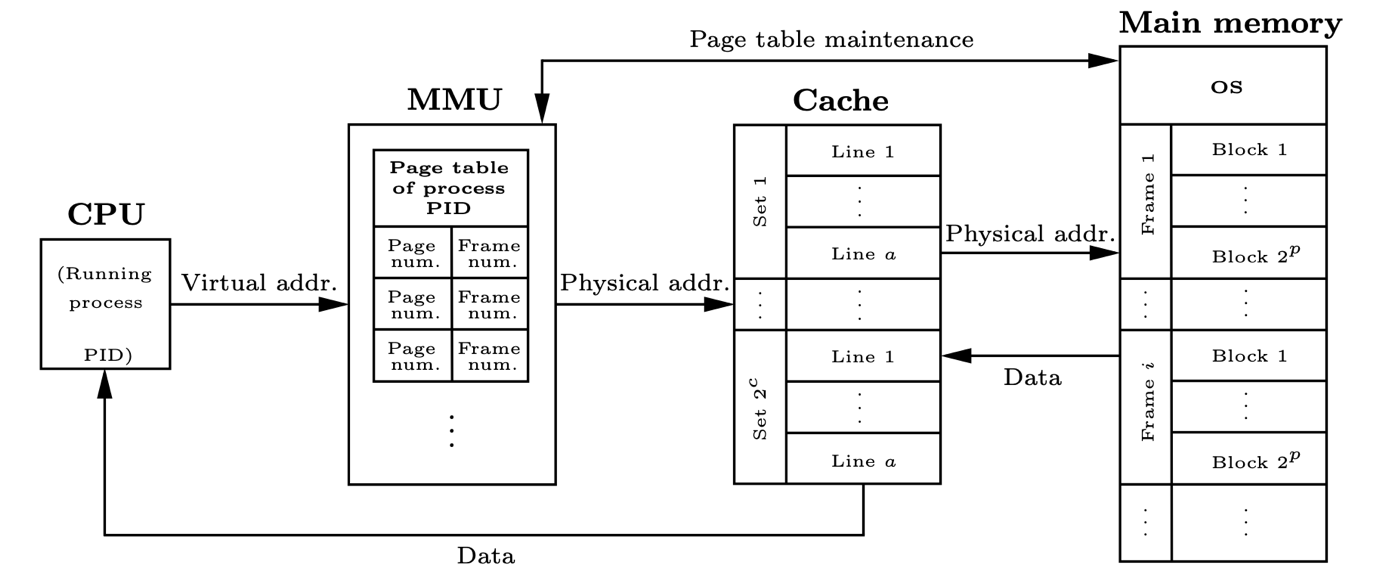

A l'arquitectura d'ordinadors, les memòria cau són components d'emmagatzematge de maquinari dissenyats per mitigar els problemes d'alta latència dels accessos a la memòria principal. La baixa latència inherent dels accessos a la memòria cau és vital per al rendiment i, tanmateix, pot provocar problemes de seguretat. De la latència d'accés es pot desprendre informació de si les dades ja residien o no a la jerarquia de la memòria cau abans de l'accés. Els atacs de canal lateral a la memòria cau permeten als adversaris obtenir informació sensible sobre els processos en execució conjunta utilitzant només mesures de latència d'accés i contenció de la memòria cau. S'ha demostrat que aquesta vulnerabilitat permet diversos atacs de microarquitectura. Una solució que té com a objectiu protegir contra atacs basats en l'accés és l'aleatorització de la memòria cau. Les memòries cau amb protecció basada en aleatorització (RPC) barregen les adreces de la memòria cau de manera que els accessos es distribueixen aleatòriament a la memòria cau. Tanmateix, s'espera que qualsevol RPC es torni insegur si els atacants tenen prou accessos.

Un dels objectius del projecte DRAC era donar solucions de maquinari a aquest problema. En primer lloc, analitzem les propietats de seguretat dels RPC i proporcionem una nova noció de seguretat que captura la seguretat contra atacs coneguts com Prime+Probe i Evict+Probe. Aleshores, utilitzant aquesta definició, obtenim resultats que ens permeten garantir la seguretat escollint adequadament la freqüència de canvi de claus, l'algoritme de generació de claus, i l’aleatoritzador de la memòria cau, proporcionant així proves de seguretat per a RPC sota determinats supòsits.

Aquest treball es presentarà a la Conference on Cryptographic Hardware and Embedded Systems (CHES) 2022. La versió completa del document està disponible a https://eprint.iacr.org/2022/440.pdf