Nos complace anunciar que la cuarta generación de la serie de procesadores Lagarto ha sido presentada para su fabricación en el nodo tecnológico de 22 nm de Globalfoundries a través de Europractice. Este diseño está basado en el repositorio de instrucciones (ISA por sus siglas en inglés) de código abierto RISC-V y es un diseño desarrollado conjuntamente por investigadores del BSC, CIC-IPN, CNM, UAB, UB, UPC y URV.

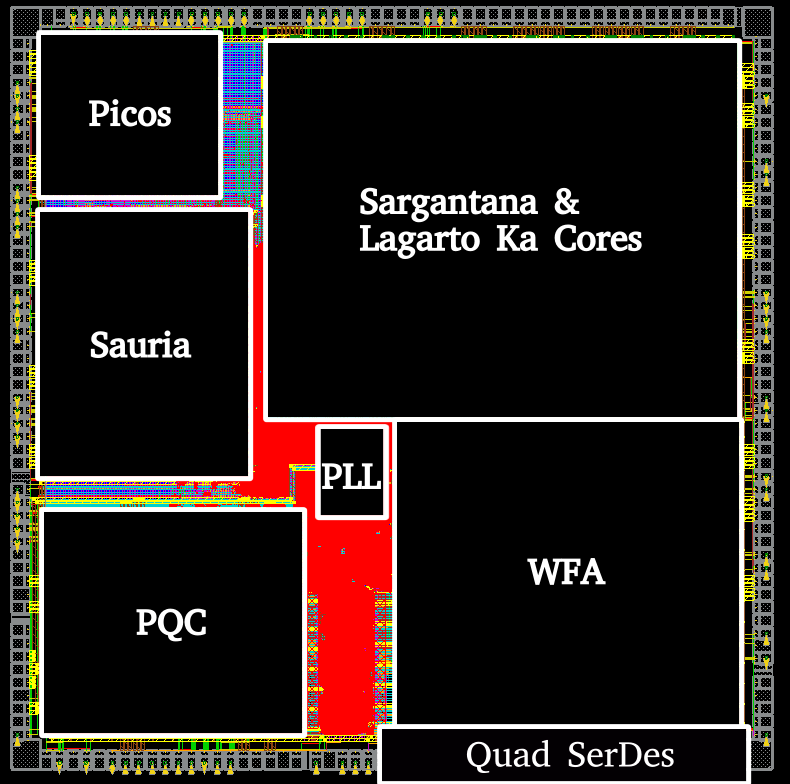

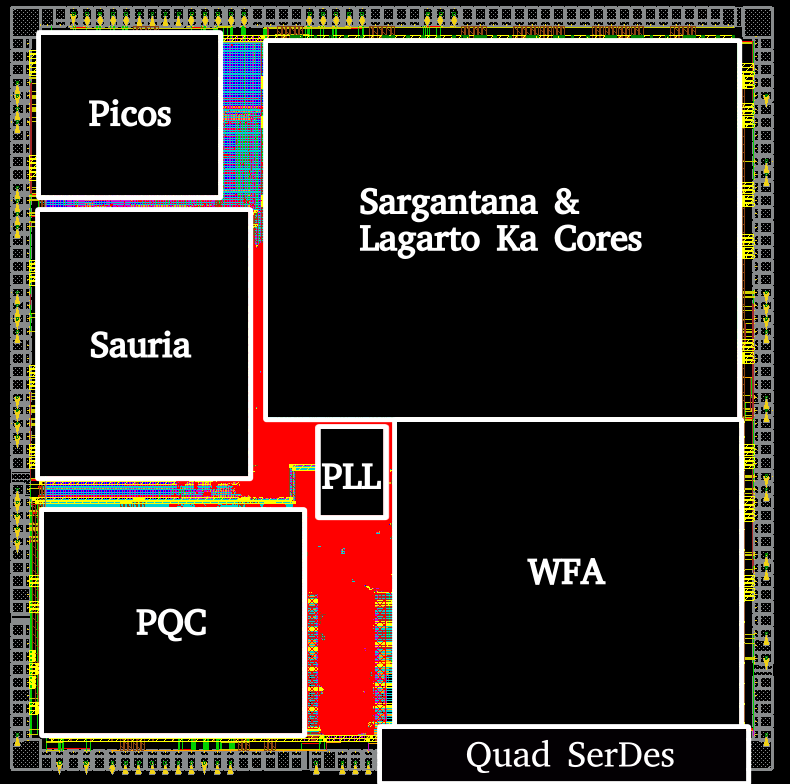

Este nuevo diseño se denomina Kameleon, ya que integra un núcleo fuera de orden Lagarto Ka junto con múltiples aceleradores de dominio específico. Como resultado, el diseño Kameleon puede cambiar su color (acelerador) en función del dominio de aplicación objetivo.

Principales novedades del diseño Kameleon con respecto a las generaciones anteriores de la serie Lagarto:

-

Nuevo diseño de núcleo con ejecición fuera de orden y doble emisión de instrucciones para conseguir un alto rendimiento.

-

Incluye un segundo núcleo para lograr eficiencia energética basado en el diseño del procesador Sargantana.

-

Memorias caché L1 y L2 más grandes para aumentar la capacidad y el rendimiento.

-

Incorporación de SAURIA, un nuevo acelerador de redes neuronales para aplicaciones de automoción basado en un diseño de matriz sistólica con cálculo aproximado para lograr una alta eficiencia energética.

-

Se ha añadido WFAsic, un nuevo acelerador para aplicaciones genómicas con una implementación personalizada para el algoritmo Wavefront Alignment (WFA).

-

Se ha añadido PQC, un nuevo acelerador para el cifrado y descifrado de criptografía poscuántica basado en el esquema Classic McEliece.

-

Se ha añadido PICOS, un nuevo acelerador para la programación de tareas por hardware en el procesador RISC-V y los aceleradores.

-

Se ha añadido un controlador de memoria SerDes de alta velocidad de cuatro canales (entre 2 y 8 Gbps).

Detalles del System-on-Chip (SoC) de Kameleon:

-

Diseño escalar Lagarto Ka, segmentado en 10 etapas, fuera de orden, RV64IMA ISA, ISA privilegiada 1.11.

-

Diseño escalar Sargantana, segmentado en 7 etapas, in-order, ISA RV64IMAFD, ISA privilegiada 1.11, VPU de 128 bits para vectores enteros siguiendo la ISA 0.7.1.

-

Aceleradores específicos de dominio: SAURIA (automoción), WFAsic (genómica), PQC (seguridad) y PICOS (programación de tareas HW)

-

Bucle de enganche de fase (PLL) integrado en el chip, diseñado y simulado para funcionar entre 600 MHz y 2,2 GHz.

-

Memorias caché de instrucciones L1 propia y PMU (unidad de control del rendimiento).

-

Memorias caché L1 de datos y L2 de Untethered lowRISC versión 0.2.

-

Múltiples controladores de periféricos esenciales: JTAG, UART, SPI, bootROM, SerDes e HyperRAM.

-

Anillo de depuración propio basado en JTAG.

-

Nodo tecnológico: GF 22FDX (22nm).

-

Superficie: 9,0mm2.

Detalles del procesador de las generaciones anteriores de diseños Lagarto:

- Comunicado de prensa de la tercera generación de Lagarto (2022): https://drac.bsc.es/en/sargantana2

- Comunicado de prensa de la segunda generación de Lagarto (2021): https://drac.bsc.es/en/media/news/tech-dvino-second-generation-lagarto-processor-series-submitted-fabrication-europractice

- Comunicado de prensa de la primera generación de Lagarto (2019): https://www.bsc.es/news/bsc-news/the-bsc-coordinates-the-manufacture-the-first-open-source-chip-developed-spain