Ens complau anunciar que la quarta generació de la sèrie de processadors Lagarto ha estat presentada per a la seva fabricació al node tecnològic de 22 nm de Globalfoundries a través d'Europractice. Aquest disseny està basat en el repertori d'instruccions (ISA, per les seves sigles en anglès) de codi obert RISC-V i és un disseny desenvolupat conjuntament per investigadors del BSC, CIC-IPN, CNM, UAB, UB, UPC i URV.

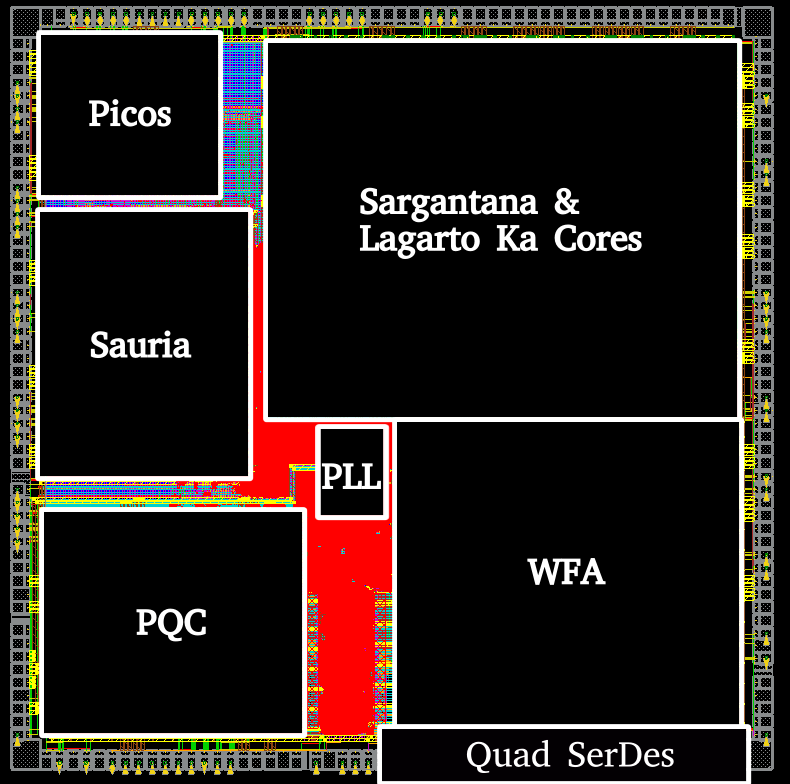

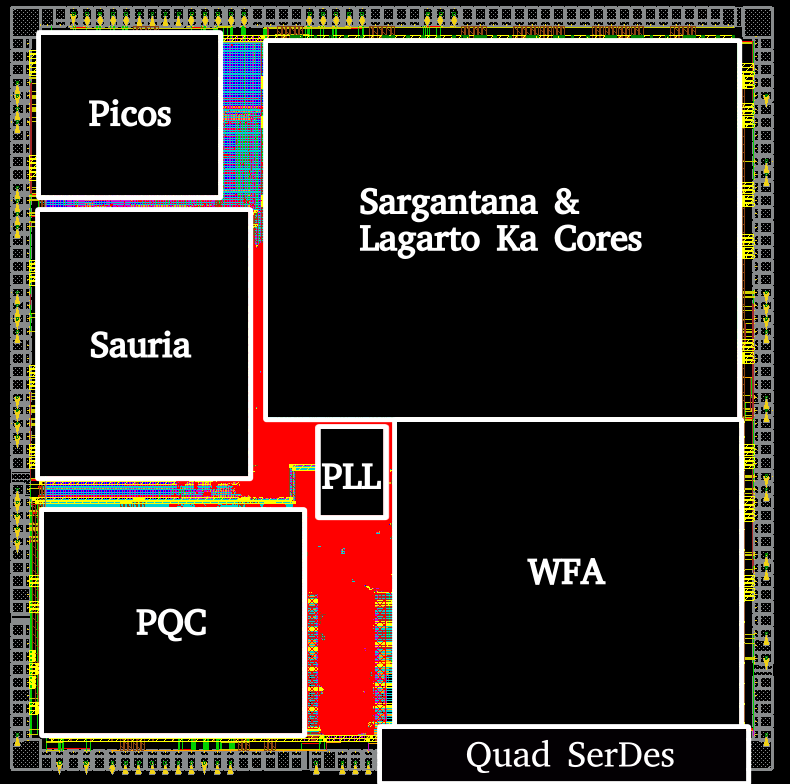

Aquest nou disseny s'anomena Kameleon, ja que integra un nucli fora d'ordre Lagarto Ka juntament amb múltiples acceleradors de domini específic. Com a resultat, el disseny Kameleon pot canviar el color (accelerador) en funció del domini d'aplicació objectiu.

Principals novetats del disseny Kameleon respecte a les generacions anteriors de la sèrie Lagarto:

- Nou disseny de nucli amb execució fora d'ordre i doble emissió d'instruccions per aconseguir un alt rendiment.

- Inclou un segon nucli per assolir eficiència energètica basat en el disseny del processador Sargantana.

- Memòries cache L1 i L2 més grans per augmentar la capacitat i el rendiment.

- Incorporació de SAURIA, un nou accelerador de xarxes neuronals per a aplicacions d'automoció basat en un disseny de matriu sistòlica amb càlcul aproximat per assolir una alta eficiència energètica.

- S'hi ha afegit WFAsic, un nou accelerador per a aplicacions genòmiques amb una implementació personalitzada per a l'algorisme Wavefront Alignment (WFA).

- S'hi ha afegit PQC, un nou accelerador per al xifratge i desxifrat de criptografia postquántica basat en l'esquema Classic McEliece.

- S'ha afegit PICOS, un nou accelerador per a la programació de tasques per maquinari al processador RISC-V i als acceleradors.

- S'ha afegit un controlador de memòria SerDes d'alta velocitat de quatre canals (entre 2 i 8 Gbps).

Detalls del System-on-Chip (SoC) de Kameleon:

- Disseny escalar Lagarto Ka, segmentat en 10 etapes, fora d'ordre, RV64IMA ISA, ISA privilegiada 1.11.

- Disseny escalar Sargantana, segmentat en 7 etapes, in-order, ISA RV64IMAFD, ISA privilegiada 1.11, VPU de 128 bits per a vector enters seguint la ISA 0.7.1.

- Acceleradors específics de domini: SAURIA (automoció), WFAsic (genòmica), PQC (seguretat) i PICS (programació de tasques HW)

- Bucle d'enganxall de fase (PLL) integrat al xip, dissenyat i simulat per funcionar entre 600 MHz i 2,2 GHz.

- Memòries cache d'instruccions L1 pròpia i PMU (unitat de control del rendiment).

- Memòries cache L1 de dades i L2 d'Untethered lowRISC versió 0.2.

- Múltiples controladors de perifèrics essencials: JTAG, UART, SPI, bootROM, SerDes i HyperRAM.

- Anell de depuració propi basat en JTAG.

- Node tecnològic: GF 22FDX (22nm).

- Superfície: 9,0mm2.

Detalls del processador de les generacions anteriors de dissenys Kameleon:

Comunicat de premsa de la tercera generació de Lagarto (2022): https://drac.bsc.es/en/sargantana2

Comunicat de premsa de la segona generació de Lagarto (2021): https://drac.bsc.es/en/media/news/tech-dvino-second-generation-lagarto-processor-series-submitted-fabrication-europractice

Comunicat de premsa de la primera generació de Lagarto (2019): https://www.bsc.es/news/bsc-news/the-bsc-coordinates-the-manufacture-the-first-open-source-chip-developed-spain