En el disseny del primer xip del projecte (Sargantana) han participat 3 grups del projecte DRAC: Barcelona Supercomputing Center (BSC), Universitat Politècnica de Catalunya (UPC) i la Universitat de Barcelona (UB). A més, també han participat l’Instituto Politécnico Nacional (IPN) i l’Institut de Microelectrònica de Barcelona (IMB-CNM), en particular el grup ICAS (Integrated Circuits and Systems).

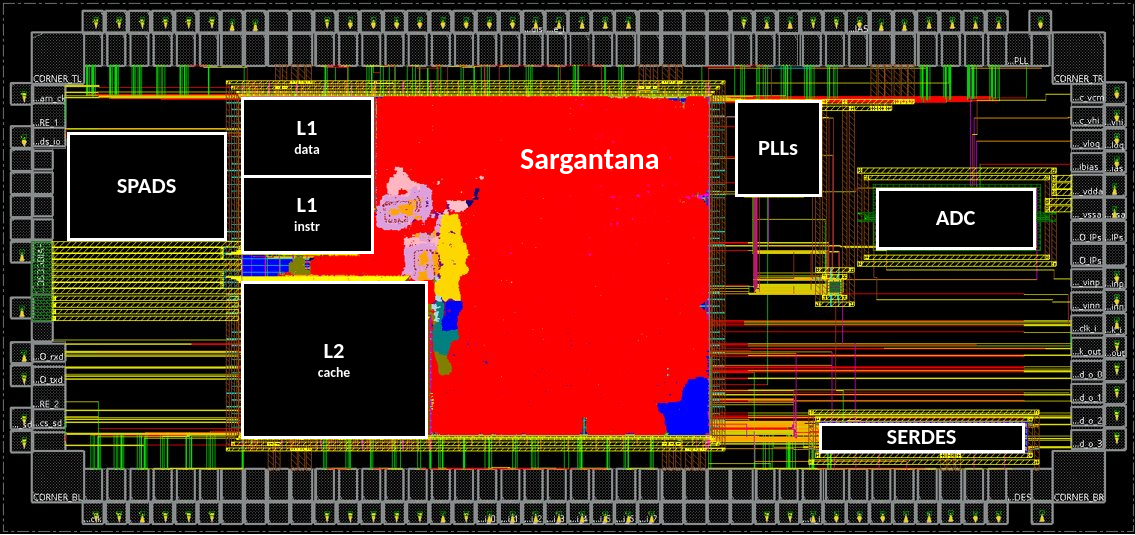

El primer xip dissenyat en el projecte es va enviar a fabricar el 18 de febrer de 2022. El xip es mostra a la Figura 1a, té una mida de 2.49 mm d’ample per 1.17 mm d’alt, el que fa una àrea total de 2.91 mm2, i ha estat dissenyat en la tecnologia de 22 nm de GlobalFoundries. A part del processador RISC-V Sargantana dissenyat en el projecte, el xip integra diferents dissenys necessaris per al correcte funcionament del processador. Aquests circuits es mostren en la Figura 1b.

El xip pretén caracteritzar les IPs subministrades per Synopsys, com les memòries i les cel·les digitals, el processador Sargantana i les IPs analògiques dissenyades pels diferents grups involucrats en el projecte. La contribució de cada grup de recerca al xip (Figura 1b) es detalla a continuació:

Sargantana: Processador RISC-V, dissenyat pel BSC i IPN, amb un pipeline de 7 etapes, utilitza la ISA (de l'anglès Instruction Set Architecture) RV64IMAFD y conté una unitat vectorial d'enters per a genòmica. El processador inclou memòries subministrades per Synopsys. Més detalls del processador es poden trobar en el següent link.

Phase-locked loop (PLL): Un PLL és un circuit per generar un rellotge a alta freqüència per al processador. En aquest xip s'han integrat dos PLLs, cosa que ens permet tenir una solució extra en cas que un no funcioni correctament. Els PLL han estat dissenyats pel grup ICAS de l'IMB-CNM i per la UPC respectivament.

SerDes: Un SerDes, o serialitzador/deserialitzador, és un circuit utilitzat en comunicacions d'alta freqüència. Aquest circuit ha estat dissenyat per la UPC.

Convertidor Analògic/Digital: Disseny del grup ICAS de l'IMB-CNM, prèviament publicat al següent link.

Bloc de configuració SPI: Disseny del grup ICAS de l'IMB-CNM que permet configurar les diferents IPs analògiques.

Single Photon Avalanche Diodes (SPADs): Els SPADs són fotodetectors d'estat sòlid i poden ser usats per generar números aleatoris. El grup de disseny de la UB ha integrat un parell d'estructures SPAD al xip.

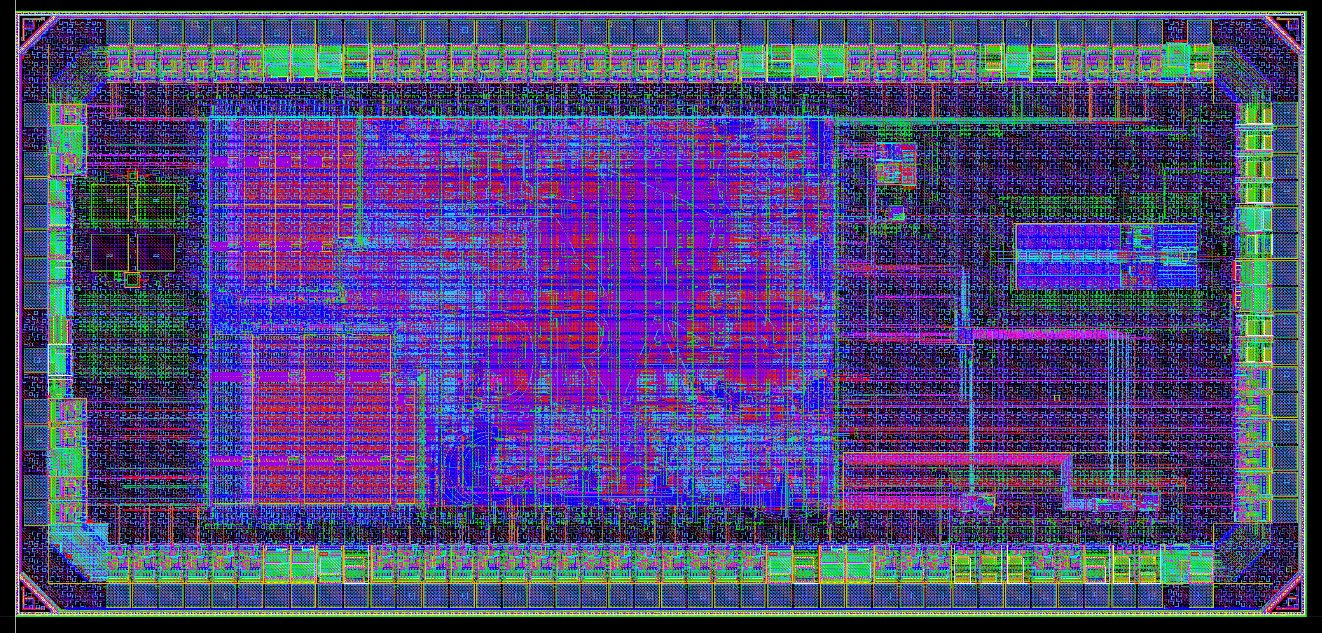

Síntesis Física: La síntesis física del xip s'ha dut a terme per la UB, detalls sobre els passos seguits en el “place & route” (és a dir, col·locar els diferents blocs, connectar-los i comprovar que el disseny compleix les normes de disseny del fabricant) es poden trobar en el següent link. Després d’aquestes etapes, es van realitzar dos passos addicionals: anàlisi de temps estàtic (STA) i l’anàlisi de potència.

Per als estudis STA, es va crear un model amb els elements paràsits del xip per estudiar si el disseny compleix les limitacions de temps imposades pels dissenyadors. Els resultats mostren que el processador pot funcionar a una freqüència de fins a 1.4 GHz.

Els estudis d’anàlisi de potència es realitzen assumint que el processador té una activitat del 10% i comprovant el consum estàtic per al millor, típic i pitjor cas a diferents temperatures. En tots aquests casos, els resultats mostres que la distribució de potència és correcta i la caiguda d’IR es pot corregir.